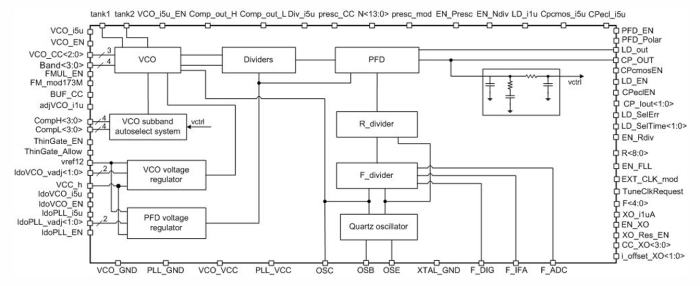

PLL is an automatic control system adjusting controlled oscillator frequency to be equal to reference oscillator frequency multiplied by a given integer. Frequency adjustment is carried out by using negative feedback. A phase detector compares a controlled oscillator output with a reference signal. The result is a charge pump current output that supplies external feedback filter and converted to a voltage for controlled oscillator adjustment. Clock frequency divider is used to generate a signal with frequency equal to reference frequency divided into integer number.

The block is fabricated on iHP SiGe BiCMOS 0.25 um (SGB25V) technology.

Frequency synthesizer 20 to 300 MHz

Overview

Key Features

- iHP SGB25V

- Wide frequency range (120…950 MHz)

- Operating frequency selection using external components

- Built-in switched capacitor sections for VCO frequency adjustment

- Low noise figure

- High lock detector accuracy

- Charge pump low output current disbalance

- Built-in reference frequency oscillator

- Programmable clock frequency divider

- Portable to other technologies (upon request)

Block Diagram

Applications

- Portable transmitters

- Portable transceiver

Deliverables

- Schematic or NetList

- Abstract model (.lef and .lib files)

- Layout view (optional)

- Behavioral model (Verilog)

- Extracted view (optional)

- GDSII

- DRC, LVS, antenna report

- Test bench with saved configurations (optional)

- Documentation

Technical Specifications

Short description

Frequency synthesizer 20 to 300 MHz

Vendor

Vendor Name

Foundry, Node

iHP SiGe BiCMOS 0.25 um

Maturity

Silicon proven

Availability

Now

Related IPs

- 20 to 300 MHz frequency synthesizer

- 7 to 20 MHz Intermediate frequency amplifier

- 1 – 600 MHz frequency synthesizer

- Input 12MHz, output 900 MHz/1200MHz, 600 MHz/800 MHz, 360 MHz/480MHz, 300 MHz/400MHz, frequency synthesizable PLL; UMC 55nm SP/RVT LowK Logic Process

- 50-800 MHz phase-locked loop frequency synthesizer

- 1 to 50 MHz phase-locked loop frequency synthesizer