UCIe IP

UCIe IP Cores (Universal Chiplet Interconnect Express) facilitate high-bandwidth communication between heterogeneous chiplets, in a single package.

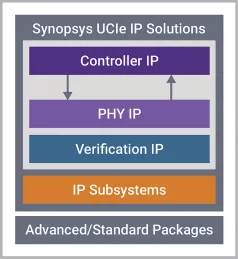

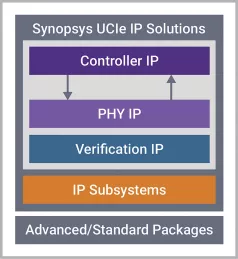

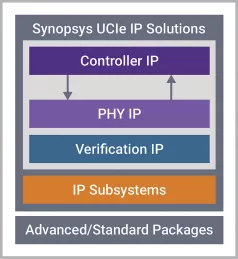

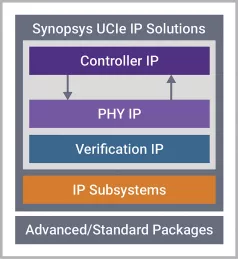

The UCIe™ physical layer includes the link initialization, training, power management states, lane mapping, lane reversal, and scrambling. The UCIe™ controller includes the die-to-die adapter layer and the protocol layer. The adapter layer ensures reliable transfer through link state management and parameter negotiation of the protocol and flit formats. The UCIe™ architecture supports multiple standard protocols such as PCIe, CXL and streaming raw mode.

Explore our vast directory of UCIe IP Cores below.

All offers in

UCIe IP

Filter

Compare

9

UCIe IP

from

4

vendors

(1

-

9)

Filter:

- TSMC

- 3nm

-

UCIe-S PHY for Standard Package (x32) in TSMC N3P, East/West Orientation

- Supports data rates up to 40Gb/s and bandwidth density of 12.9Tbps/mm

- Compliant with the latest UCIe specification

- Integrated signal integrity monitors and comprehensive test and repair features

- Supports high-density advanced packaging technologies such as silicon interposer, silicon bridge, and RDL fanout

-

UCIe-A PHY for Advanced Package (x64) in TSMC N3E, North/South Orientation

- Supports data rates up to 40Gb/s and bandwidth density of 12.9Tbps/mm

- Compliant with the latest UCIe specification

- Integrated signal integrity monitors and comprehensive test and repair features

- Supports high-density advanced packaging technologies such as silicon interposer, silicon bridge, and RDL fanout

-

UCIe-S PHY for Standard Package (x32) in TSMC N3P, North/South Orientation

- Supports data rates up to 40Gb/s and bandwidth density of 12.9Tbps/mm

- Compliant with the latest UCIe specification

- Integrated signal integrity monitors and comprehensive test and repair features

- Supports high-density advanced packaging technologies such as silicon interposer, silicon bridge, and RDL fanout

-

UCIe-S PHY for Standard Package (x16) in TSMC N3E, North/South Orientation

- Supports data rates up to 40Gb/s and bandwidth density of 12.9Tbps/mm

- Compliant with the latest UCIe specification

- Integrated signal integrity monitors and comprehensive test and repair features

- Supports high-density advanced packaging technologies such as silicon interposer, silicon bridge, and RDL fanout

-

UCIe-S 64GT/s PHY IP

- The UCIe-S 64GT/s PHY IP is a cutting-edge solution designed to meet the growing demand for ultra-high-speed interconnects between dies in standard packaging environments.

- Leveraging the UCIe (Universal Chiplet Interconnect Express) 3.0 standard, this IP supports a blistering data rate of up to 64Gbps per lane, enabling next-generation AI, HPC, and data center SoC applications.

-

Chiplet Interconnect - Die-to-die interconnect IP solutions for advanced and standard packaging applications

- High data rate of 2–24 Gb/s

- Very low power of < 0.375 pJ/bit @ 2–16 Gb/s 0.5-V VDDQ

- Very low latency of < 2 ns PHY-to-PHY

- Support for 2:1, 4:1, 8:1, 12:1 and 16:1 serialization and deserialization ratios

-

UCIe-S PHY for Standard Package (x32) in TSMC (N3P)

- Data rates up to 16Gbps per pin

- Self-contained hard macro

- Self-calibrating and training

- Side band channel for initialization and parameter exchange

-

UCIe-S PHY for Standard Package (x16) in TSMC (N7, N6, N4P, N5, N3)

- Data rates up to 16Gbps per pin

- Self-contained hard macro

- Self-calibrating and training

- Side band channel for initialization and parameter exchange