Building Blocks IP

Welcome to the ultimate Building Blocks IP hub! Explore our vast directory of Building Blocks IP

All offers in

Building Blocks IP

Filter

Compare

369

Building Blocks IP

from 51 vendors

(1

-

10)

-

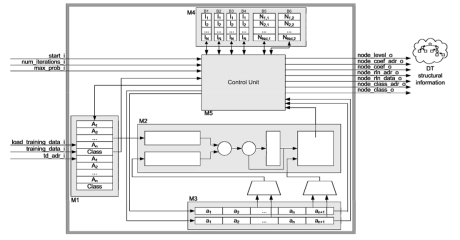

Decision tree inference core

- So_ip_idt core can be used create a decision tree directly in hardware. It can create DTs with univarite, multivariate and non-linear tests.

- Creating DTs directly in hardware results in the significant increase of DT inference speed, compared with the traditional software-based approach.

-

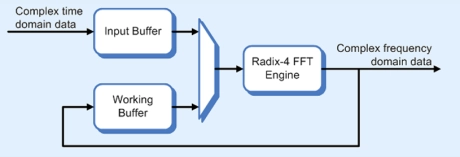

General-purpose FFT core

- The FFT is factored into Radix-4 Butterfly operations. When an odd power of two is required, a small radix-2 “follower” stage performs the final iteration. The radix-2 stage does not require a full complex rotator so its cost is minimal.

- The Radix-4 Engine fetches one complex word of data each clock cycle. Four interleaved data words are collected then applied to the t0-t3 inputs. On successive clock cycles the engine calculates the four frequency domain outputs f0-f3. These are then stored back into the Working Buffer.

-

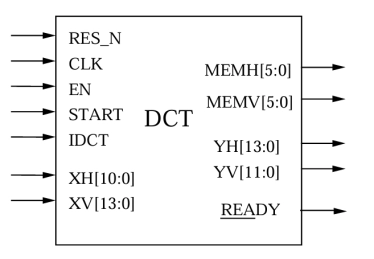

Discrete Cosine Transform

- This core can perform the two dimensional Discrete Cosine Transform (DCT) and its inverse (IDCT) on an 8x8 block of samples.

- The simple, fully synchronous design allows for fast operation while maintaining a low gate count.

- It offers high performance and many features to meet your multimedia, digital video and digital printing applications

-

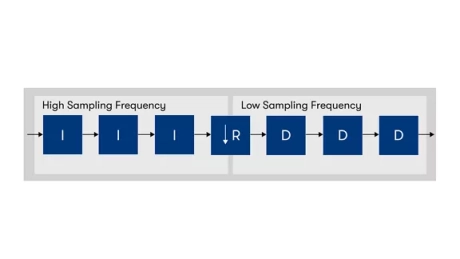

CIC Intel® FPGA IP Core

- The CIC Intel FPGA IP core implements a Cascaded integrator-comb (CIC) filter with data ports that are compatible with the Avalon® streaming (Avalon-ST) interface

- CIC filters (also known as Hogenauer filters) are computationally efficient for extracting baseband signals from narrow-band sources using decimation

- They also construct narrow-band signals from processed baseband signals using interpolation.

-

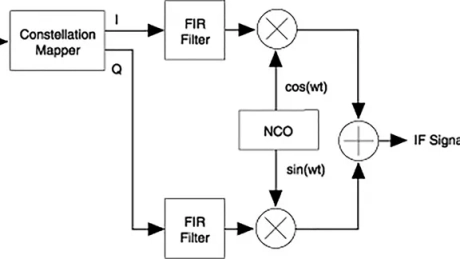

NCO Intel® FPGA IP Core

- A numerically controlled oscillator (NCO) is a digital signal generator, which synthesizes a discrete-time, discrete-valued representation of a sinusoidal waveform

- You can typically use NCOs in communication systems

- In such systems, they are used as quadrature carrier generators in I-Q mixers, in which baseband data is modulated onto the orthogonal carriers in one of a variety of ways.

-

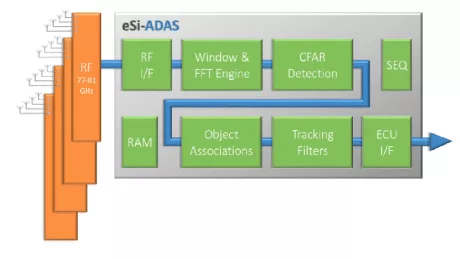

Radar processing IP suite for Advanced Driver Assistance Systems

- The eSi-ADAS™ is a suite of radar accelerator IP including a complete Radar co-processor engine, they enhance the overall performance and capabilities of radar systems for automotive, drone and UAV applications that require fast and responsive situational awareness.

- The IP has been licensed to some of the leading automotive Tier 1 and Tier 2 suppliers and is in production vehicles.

-

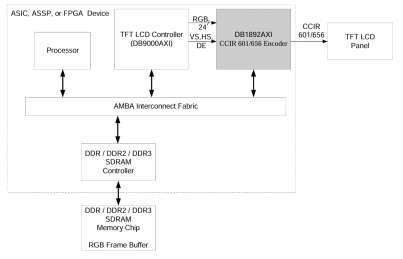

RGB to ITU-R 601/656 Encoder

- The DB1892AXI RGB to CCIR 601 / CCIR 656 Encoder interfaces RGB data along with synchronization signals from a LCD Controller (or any LCD display timing & control unit) to a TFT LCD Panel by-way-of a CCIR 601 / CCIR 656 interface.

-

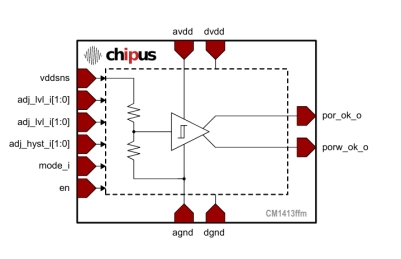

Power-On Reset - Flexible Threshold (1-1.3V), Ultra Low Current (100nA) - SilTerra 0.16µm CL160G

- This macro-cell is an ultra low consumption Power-On Reset (POR) core designed for SilTerra 0.16μm CL160G CMOS technology.

- The threshold sensing voltage can be configured from 1V to 1.3V (default is 1.15V). A hysteresis of 120mV is added to avoid false reset glitches in noisy supplies.

-

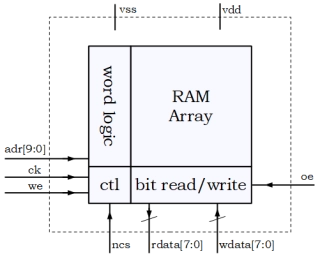

RAM 8b, 16b, and 32b data widths - TSMC 180nm

- 8b, 16b, and 32b data widths available.

- Up to 250MHz clock operation.

- Read and write data busses may tie for single bus operation.

- Available production test RTL.

- VDD 1.6V – 2.0V.

- Data retention to 0.9V.

-

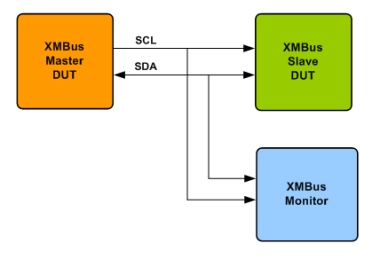

XMBus Verification IP

- Supports XMBus specifications version 0.5.

- Supports XMBus device types: Master, Slave.

- Start, repeated start and stop for all possible transfers.

- Supports 7bit configurable Slave address.