Other

All offers in

Other

Filter

Compare

192

Other

from

25

vendors

(1

-

10)

-

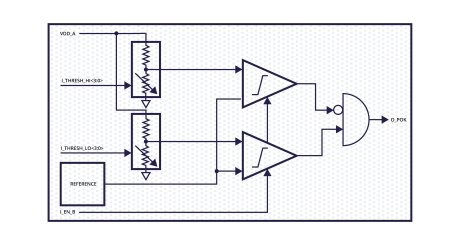

Power-OK Monitor

- The agilePOK is a Power OK monitor that consists of a voltage reference and comparators to set a programmable high and low threshold level for power supply integrity detection.

- The number of trigger outputs can be customized and each threshold can be adjusted during operation to support DVFS operation.

- This monitor can be used to detect loss of power or attacks to the power supply.

-

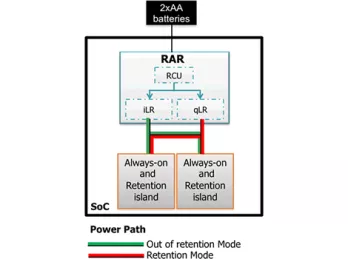

Retention Alternative Regulator, combines a linear regulator and an ultra-low quiescent regulator for sleep mode

- Ideal regulator for power and voltage islets

- Secured integration in the SoC Embedded RCU (Regulator Control Unit) to manage booting and mode transitions and to ensure data integrity

- Configurable output drive before delivery to fit the application

- Performances in sleep mode: qLR with low quiescent current: 0.2 uA

-

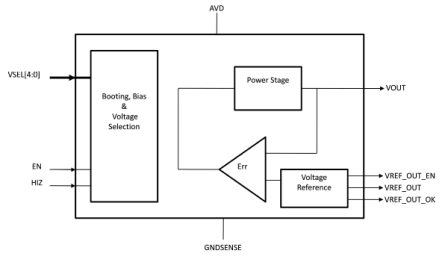

Linear Regulator, ultra low quiescent current for retention mode TSMC 40uLPeF

- qLR-Aubrey-ref-1.62-3.63-0.55-2.5.02_TSMC_40_uLPeF is an ultra-low quiescent LDO (Linear regulator) in TSMC 40uLPeF.

-

Linear Regulator, ultra low quiescent current for retention mode

- Very low quiescent and leakage for Low-Power

- Retention capability enables optimization of the power consumption depending on the modes and needs of the SoC

- Can supply always-on very low loads

- Low Bill-of-Material: supports external capacitor if required by the system

-

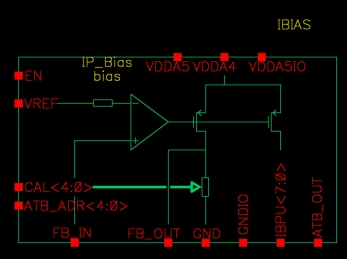

Octuple 20uA Bias Current Source

-

The TS_CS_20uA_X8 is a current generator sourcing 20µA via each terminal IBPU<0> through IBPU<7>, for the biasing of other TES IPs like TS_FS_9M70_X8 and TS_VA_LNDC_X8 (for the latter IP, its input reference current must be mirrored from one Bias output by a simple cascoded NMOS circuit)

-

-

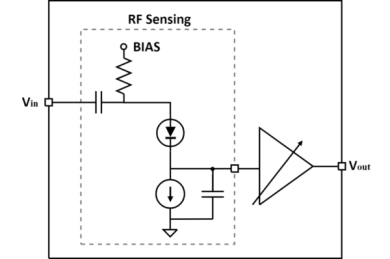

Ka Band power detector

- The WEAKA01PD22G is a power detector capable of detecting signals in the range of 3 dBm to 18 dBm with an accuracy of +/-0.5 dB

- It produces a voltage proportional to the received signal power with the maximum output voltage being 1.1 V

- It consists of 2 parts, the RF and the Analog processing part

- Multiplexing can also be used to support multiple RF inputs with minimal impact on the silicon area using the same analog part

-

Linear Li-Ion Battery Charger - Programmable charging current up to 1.1A Fast Charge - SilTerra 0.18um

- This USB/AC Li-Ion battery charger is targeted for portable applications.

- The charging current can be adjusted from 60mA up to 1.1A through an external resistor or by digital control.

- The current provided to the system can also be adjusted up to 1.8A through the same procedure.

-

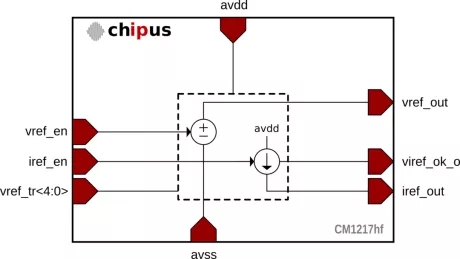

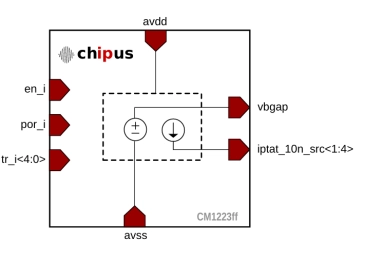

ULP Bandgap Voltage Reference - 210nA consumption, 40ppm/ºC - Silterra 0.18um

- This macro-cell is an ultra-low-power bandgap voltage reference (1.23V) with low temperature coefficient (>40ppm/ºC) consuming 210nA.

- A 5-bit digital bus allows TC adjust against process variations. It provides a built-in 10nA PTAT current reference with 4 outputs.

-

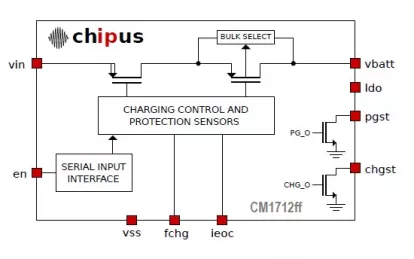

Linear Li-Ion Battery Charger - ±1% Accuracy (4.2V) / Up to 1.1A Fast Charge SilTerra 0.18um

- This USB/AC Li-Ion battery charger is targeted for portable applications.

- The full current charge can be set from 100mA to 1.1A. It provides a regulated voltage of 4.2V for powering external loads up to 2.3A in the absence of the battery.

- The recommended supply input voltage range is 4.5V to 6.9V, however the battery charger can support from 3.3V up to 30V in idle mode.

-

Low-Noise Bandgap Reference - Low Noise: 63nV/√Hz, PSRR: -80dB - TSMC 0.18um CMOS (CLM18)

- This macro-cell is a low noise, high PSRR voltage reference core designed for TSMC 0.18um (CLM18) CMOS technology.

- The core is ideal for applications where noise performance is critical.

- The circuit generates a buffered 1.185V, temperature-compensated bandgap voltage reference (40ppm/°C).