Traceability Complements Agile Design

作者:Paul Graykowski, 高级技术营销经理, Arteris IP

敏捷设计方法已成为软件开发的主流,因为传统的瀑布式方法无法适应大型、快速变化的产品计划。系统级芯片(SoC)开发团队已经注意到这一点,并积极采用类似的方法来加快进度,更加灵活地应对过程中的需求变化。但是,敏捷方法必须得到敏捷验证/确认 (V&V) 的支持,以确保快速发展的开发始终朝着正确的方向前进。 V&V 必须得到适应性测试和需求确认的支持。

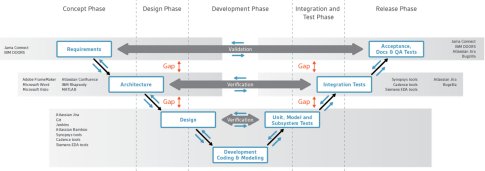

图1.系统开发、验证和确认示意图

SoC设计中的敏捷

今天的产品定义和时间表都受到快速发展的市场的影响 – 比如汽车、通信、工业自动化、高性能计算 (HPC) 和物联网 (IoT)。新产品创意不断追求新的可能性,许多是在消费者驱动的领域,通常在赢家通吃的市场。持续多年的产品开发周期成为遥远的记忆。市场压力要求在一年或更短的时间内从概念过渡到产品,包括 SoC 和支持软件。

对于 SoC来说,软件团队可能已经在敏捷流程中工作。设计师最接近客户的系统需求,也最容易受到变更的影响。其中一些变更也会影响到 SoC,例如需要添加或更改控制和状态寄存器。尽管如此,如果 SoC 级别的需求不能满足规范并且可以替代实现,它将被送回软件团队。与需求保持同步的责任被分配给软件和 SoC 团队,甚至进一步分配给 IP 团队。

这是一种动态的需求反复,正是敏捷方法定义的产品发展类型。敏捷提供了支持动态需求的方法,但是如何使软件和 SoC 开发与不断发展的规范保持同步呢?

使开发与需求保持联系

回归测试是确认进程持续符合需求的重要部分。在上面的图 1 中,V 形图显示随着设计沿左侧发展,测试会沿右侧发展。然而,回归测试不能成为保持敏捷设计走在正轨上的唯一资源。测试本身需要时间来开发和调试。在某些关键功能可用之前,可能无法交付测试。一些需求取决于用例对性能的理解,这可能很难完全验证。

举一个具体的例子,考虑在状态寄存器位域中需要一个标志。最初指定设计时,系统设计意图是,这个通过硬件操作设置的标志将用于通知一个或多个软件进程已完成特定步骤。当所有请求程序都得到满足时,另一个软件功能将清除该标志。硬件设计按照这一要求进行。在之后的软件开发中,很明显,这个测试对某一个软件请求程序处于性能关键循环中,而其他软件请求程序在通过另一个路径来获取这些数据时可以承受额外的延迟。关键请求程序需要排除所有可能的延迟来变更位域的硬件需求。因此它必须在读取时清晰明确,避免需要软件触发的复位,并节省许多周期。

从硬件设计的角度来看,这是一个非常低级别的后期需求更改,很容易被忽略。如果该更改能尽快被辨识认可,实现起来可能并不困难。这个过程可能需要额外的布线、额外的逻辑、时钟和复位更改,对电源管理进行调整,以及验证和布局图的返修。更改的需要可能是不可避免的,但它不能被淹没在噪声中,并且必须尽快了解其对硬件的影响。

测试必须由设计者和验证者对规范变化的实时理解来补充。这种理解可以通过自动化需求跟踪来保证。通过像 Jama Connect 和 IBM DOORS这样的工具,这种能力已经在软件领域得到了很好的支持。然而,这些工具对硬件领域的跟踪没有本机理解。这些资源提供了超越软件但没有硬件设计语义的跟踪机制。使用这种方法需要 SoC 设计人员进行大量的工作和检查,从而削弱了跟踪的很大部分价值。

理想情况下,设计和验证团队应该创建一个敏捷系统,该系统在 V-V 图表的每个组件中包含最适合工作的工具。然后,该团队充分利用自动化将需求连接并跟踪到设计、验证和确认工件。需求需要保持近乎实时的可追溯性,以便团队可以立即检测到变更并适当做出反应。在管理人员检查整个产品的需求合规性时,最大程度地利用了一流的软件跟踪工具。这超越了软件检查,进入 SoC 领域,而无需全面了解 SoC 实现的知识。Arteris IP® Harmony Trace™ 提供了这样一套系统,使敏捷方法能够扩展到整个产品开发过程中。

敏捷开发中是否需要可追溯性?

在某些领域,可追溯性是合规性的需求。然而,总的来说,敏捷开发流程的价值现在是一个重要的话题。一位消息人士进行了研究,以显示可追溯性的完整性和软件缺陷率之间存在明确的联系。在设计和测试中,如果经常提醒设计人员注意需求,那么就更有可能遵循规范。此外,研究表明,在需求跟踪的指导下,开发人员可以更快地完成任务。

总之,可追溯性可以成为 SoC 开发中敏捷实践的宝贵补充。回归测试很重要,但是等待完整并且经过调试的测试会影响敏捷方法的价值。需求可追溯性弥补了缺失和不完整测试的不足,并恢复了敏捷性。要了解更多关于使用 Harmony Trace 将敏捷和可追溯性扩展到 SoC 设计的信息,请点击这里。

Paul 是 Arteris IP 的高级技术营销经理,在SoC的设计和验证方面拥有超过 20 年的经验。在加入 Arteris 之前,Paul 专门研究验证方法,专注于最终成为 SystemVerilog 和 UVM 的技术。在他的职业生涯中,他曾在 Compaq、Intel 和 Synopsys 担任过多个职位,包括设计咨询、产品和方法专家、技术和产品营销,以及应用工程领导。 Paul 拥有德州农工大学的 电子工程学士学位。

Related Semiconductor IP

- Verification IP for I3C/I2C

- Verification IP for SATA

- Verification IP for SAS

- Verification IP for DisplayPort/eDP/DSC/DPI

- Verification IP for HDMI