Traceability for Embedded Systems

作者:Paul Graykowski

对于大多数人来说,可追溯性可能是一个模糊难懂和/或比较官僚的概念。它需要在电子表格、规范与实现和验证之间交叉检查需求,不断重复。从必须解决实际问题的角度来看,很难理解这项工作如何增加价值。事实上,如果设计团队从一开始就完全理解所有需求,并在整个设计周期中始终保持这种完美理解,当为了满足功率、性能、面积 (PPA) 和其他目标而进行更改时也保持,并且系统/软件需求在此期间保持完全静止,那么整个期间,就没有必要继续保持检查。但是实际上,很少有团队经历过这样的理想项目。理解并不总是完美的,需求也很少是完全静止的。保持需求和实现之间的链接是嵌入式系统的可追溯性可以发挥价值的地方。可追溯性支持对于安全关键系统是强制性的,但在其他复杂嵌入式系统中的更广泛价值也值得评估。

通过V型图进行交叉检查

系统开发、验证和确认

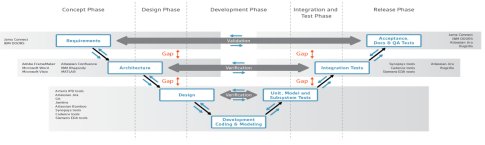

V型图被广泛使用来表示系统开发生命周期。它描绘了从概念到实现的设计演变,以及从低级测试到完整系统确认的验证过程。在开发部分(左臂),概念逐渐细化,从需求到体系架构,然后到更详细的设计,最终到设计实现。在验证部分(右臂),验证从单元测试和子系统测试开始,然后发展到集成测试,最后到完整系统确认。虽然所有这些都非常熟悉,但是该过程并没有跟踪偏离原始需求或者人工翻译错误的可能性,人工翻译错误是由于跨越V 型图中自动化岛屿之间的差距所导致的。

在嵌入式系统中,硬件/软件接口 (HSI) 代表了硬件和软件开发团队之间的需求。其文字描述详细阐述了存储器和 IP 寄存器偏移、位域和详细行为规范方面的大量细节。其中,至少某些方面必须精确满足。这种期望特别重要,因为许多设计必须使用遗留软件,不仅要最大限度地缩短开发时间,还要保持可靠性。采用来自不同供应商的新器件来替换旧器件时,必须做到全部或大部分原始 HSI一致。在这种情况下,记录这些需求并使用可追溯性来跟踪开发过程的合规性成为一个明显的优势。

可追溯性电子表格

对我们大多数人来说,显而易见的解决方案是在电子表格或像Jama Connect这样的专用工具中记录需求。在电子表格的术语中,表格中每个需求有一个条目,其中包含用来定位实现中的支持性工件(例如,文件和功能名称)的列。接下来是测试证据、所有者姓名、状态和最后检查日期等类似列。开发团队可能会建立分层次的电子表格,甚至可能按需求组分为多个文件。这是跟踪任何一种状态的标准工程实践。每个设计审查都有一部分专门用来检查这些电子表格和相应的设计组件之间的对应关系。

当必须跟踪数百个需求时,电子表格可以很好地工作。但是当需要跟踪成千上万个需求时,该方法就会失效。更糟糕的是,它没有提供任何明显的方法来识别需求的变化。这个问题可以通过使用需求跟踪工具来解决。这样的工具当然可以帮助需求开发人员,但不能帮助检查人员。检查仍然是手动进行的,并且变化可能需要更新以支持证据的位置,需要大量的手动工作。

Arteris® Harmony Trace™ – 智能可追溯性

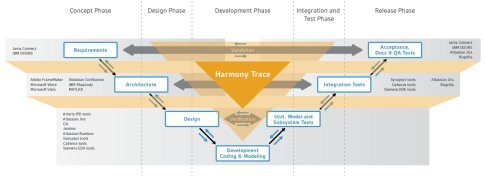

在整个系统设计范围内建立自动可追溯性时,最大的挑战是所涉及的工具和流程使用非常不同的语言。 从用于需求的 DOORS 或 Jama Connect,到用于架构的 C++,SystemC 和 Matlab。 从用于设计的寄存器传输级 (RTL) 到用于单元和块级测试的通用验证方法 (UVM),再到用于系统级验证的 Accellera开发的可移植激励标准(PSS)。 所有这些工具都辅以在线仿真和实验室测试,以进行完整系统确认。在这些领域之间建立链接需要采用一种智能方法,来建立和检查这一广泛范围内的可追溯性。 同时,需要将每个领域必须理解的内容限制为支持跟踪确认所需的内容。 Arteris IP 公司的 Harmony Trace 工具可以提供这种智能支持。

使用 Harmony Trace 弥合差距

Harmony Trace 理解并能够利用多个特定领域的标准:比如用于需求的REQ-IF,用于片上系统 (SoC) 组装和 HSI 的IP-XACT,以及用于文档的DITA。由于该工具理解每个领域的语义,因此它可以跟踪特定领域的专有技术,例如所使用的 IP 版本,以及总线的配置或宽度。它还可以记录位域是否支持简单读取,或者在读取时清除位域。此外,它还可以理解文档中的参数表,甚至需求中的参数引用,以在这些域之间进行关联。而且更进一步,当它在实现或测试中跟踪证据引用时,它会跟踪语义对象,而不是“简单”的文件/行引用,从而随着设计的发展在引用方面提供更高的可靠性。

这些功能极大地简化了设计审查检查。一旦设计团队建立了初始需求与实现和测试的链接,后续的合规性检查就变得容易得多。硬件设计人员可以直接跳转到需求证据,并确认两者是否继续提供有效支持。更好的是,有可能自动建立大多数初始链接,这将消除确保可追溯性的进一步手动工作。

想要了解更多?请点击这里下载白皮书。

Related Semiconductor IP

- Verification IP for I3C/I2C

- Verification IP for SATA

- Verification IP for SAS

- Verification IP for DisplayPort/eDP/DSC/DPI

- Verification IP for HDMI