Streamlining SoC Integration With the Power of Automation

作者:Insaf Meliane, Arteris 产品管理和营销经理

半导体技术的快速发展正在创造日益复杂的片上系统(SoC)器件。这些芯片包含数十亿个晶体管和数百个功能知识产权(IP)模块。这种爆炸式增长的复杂性需要SoC集成的自动化,这是实例化、连接和配置所有IP的过程。此过程通常包括来自可信的第三方供应商的IP和内部开发的组件,这些组件将该设计与竞争对手的产品区分开来。

第三方 IP 通常涵盖的领域包括通信功能(如以太网、USB 和 MIPI),以及中央处理器、图形处理单元、内存子系统和动态内存访问控制器。内部开发的 IP 可能包括硬件加速器和机器学习推理引擎。这些 IP 模块是异构的,具有不同的格式、不同的协议和不同的接口,需要集成到一个运行良好的 SoC 中。这种集成过程在半导体设计中提出了多方面的挑战,超越了简单的即插即用方法。

管理 SoC 集成是一项艰巨的任务,其特点是固有的复杂性,以及来自不同输入格式和来源的数据聚合可能出错。设计人员必须跨多个团队进行协作,这些团队通常分布在不同的站点,从而导致工作流程碎片化。他们的许多任务都需要大量的手动操作。SoC 设计中的这些手动流程可能容易出错且耗时,导致延迟实现上市时间的目标。这些挑战凸显了对简化和缩短 SoC 集成的标准化方法的需求。

SoC 集成中的元数据

元数据(包括有关每个 IP 的详细信息)在集成过程中起着核心作用。它提供了基本信息,从而简化了跟踪和处理特定数据的过程。传统上,这些信息是手动精心处理的,并记录在数据表或电子表格中。各个团队负责创建和维护这些文件,当设计选择未在相关团队之间有效沟通时,这通常会导致差异。

IP-XACT 用于标准化

为了应对这些挑战,IP-XACT标准作为一种通用格式被开发,与传统的HDL语言相比,以更高级别的抽象来交换和重用有关IP和子系统的信息。IP-XACT使用机器可读格式(XML),实现高效自动化,促进设计流程步骤之间的互操作性,并采用经过验证的构造校正方法(correct-by-construction methodology),确保系统高质量。它包括内置的语义一致性(Semantic Consistency)以及规则,可通过早期问题检测实现更高质量的设计。它还允许内部团队协作,确保数据一致性。为了充分利用该标准,需要正确的工具和合适的开发环境。

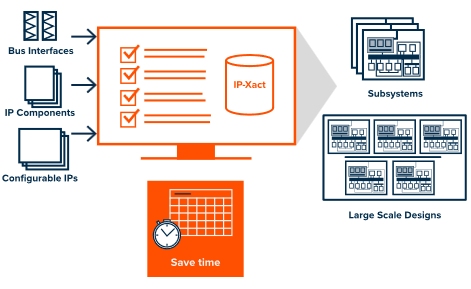

利用 Arterris 的Magillem工具可以将SoC整合过程从几个月减少到几周。

(来源: Arteris, Inc.)

转变 SoC 集成

Arteris 的Magillem工具是基于IP-XACT标准的SoC集成自动化的强大解决方案。它不仅仅是连接端口;它还配置并实例化每个IP,识别每个总线协议,从而实现正确的总线互连。 这会产生结构化的顶级 RTL 网表、EDA 工具的生成文件脚本和连接报告,使集成更加透明。这种环境使层次结构调整、升级 IP 和重组设计变得容易,使设计团队能够更灵活地适应不断变化的请求。

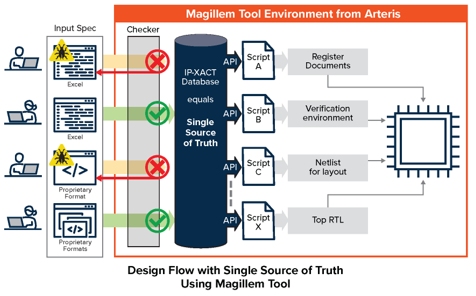

Magillem 工具作为单一事实来源,确保设计团队之间的同步,这些团队都可以有效协作,以加速 SoC 开发,同时减少设计错误。 它简化了关键任务,例如构建系统内存映射、生成无差错的 RTL 寄存器库和创建全面的文档。

Magillem工具提高SoC效率

通过将自动化整合到持续集成管道中,并为前端设计建立强大的自动化流程,Arteris利用其专业知识为设计团队提供支持,提高生产力,并确保一次性成功的项目。该公司提供了三款功能强大的产品,重新定义了SoC集成中的自动化:

Magillem Connectivity 加速了复杂系统的设计,简化了 IP 模块的集成,确保了卓越的质量,并缩短了设计周期时间。

Magillem Registers 自主构建无差错的系统内存映射,确保SoC器件的准确性和可靠性。

CSRCompiler 简化了硬件-软件接口的创建,为整个团队提供了一个完整、正确、最新的寄存器设计生态系统。

这些产品彻底改变了设计过程,使其更加高效、敏捷和准确。设计团队可以利用这些工具来最大限度地提高他们的生产力和专业知识,以无与伦比的效率提供尖端的 SoC 器件。

采用Magillem 工具作为单一事实来源的设计流程

(来源: Arteris, Inc.)

结论

在SoC集成中,自动化不再是一种选择,而是一种必需。自动化工具和像IP-XACT这样的标准是推动公司走向市场前沿的关键。

IP-XACT标准和Arteris的Magillem等工具提供了有效的解决方案。通过利用标准化元数据和自动化友好的环境,设计团队可以简化过程、降低设计风险并加快上市时间。Arteris的Magillem工具提供了一条成功的SoC集成途径,最终提高了团队的生产力和SoC设计的整体有效性。

有关Arteris 的SoC集成自动化的更多信息,请点击访问 这里。

Related Semiconductor IP

- HYPERBUS™ Memory Controller

- Verification IP for AMBA

- Verification IP for UCIe

- Verification IP for HBM

- Verification IP for Ethernet