Perceptia Updates Design Kit for pPLL03 on GlobalFoundries 22FDX Platform

Sydney, Australia — November 6, 2025 — Perceptia Devices, a leader in high-performance clocking IP, today announced the availability of an updated design kit for its pPLL03 phase-locked loop IP on GlobalFoundries’ 22FDX® (22nm FD-SOI) technology node.

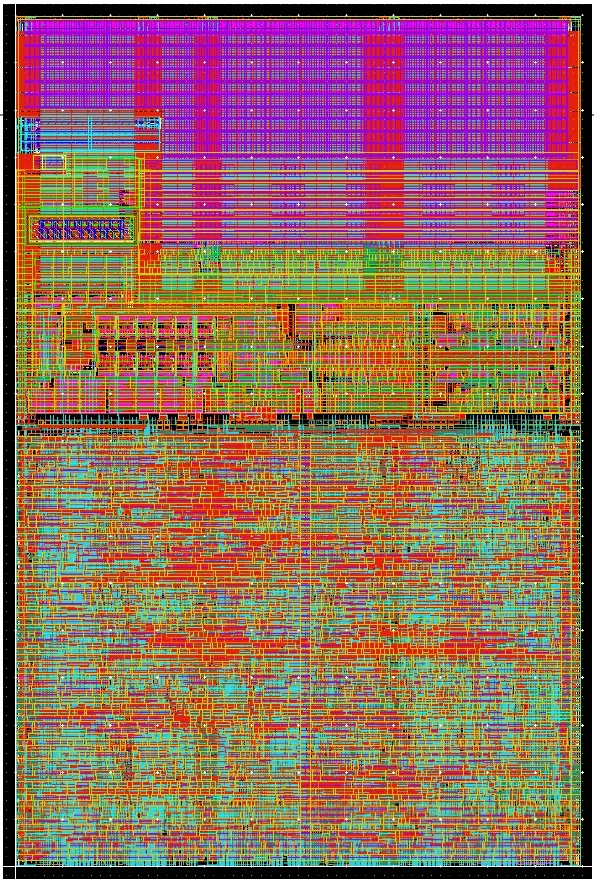

The pPLL03 is Perceptia’s low jitter, high-performance PLL IP core targeted at demanding SoC applications including AI accelerators, microprocessors, ADC/DAC sampling clocks, and high-speed digital subsystems. The release of the design kit enables SoC developers to efficiently incorporate the pPLL03 into their designs with full support for layout, simulation, and timing closure.

This update upgrades pPLL03 to include a power conditioning circuit that makes it more tolerant to power supply noise and allows pPLL03 to be more reliable in a range of environments.

Key technical features of the pPLL03 include:

- Output frequency range: Up to 4 GHz, supporting integer and fractional-N operation

- Peak Period Jitter: Less than 2.1% of a cycle at 4GHz (5.25ps)

- Fast lock time (400 reference clock cycles)

- Fractional output division for rapid frequency change with glitch-less transition and 6 bit fractional resolution suitable for dynamic frequency scaling

- Compact footprint: Highly area-efficient implementation with minimal analog overhead.

- 0.008 sq mm in GF 22FDX

- Robust behaviour across process, voltage, and temperature extremes

The pPLL03 supports both integer-N and fractional-N synthesis, allowing for fine-grained frequency generation. Its all-digital control interface enables easy integration with standard digital flows and software-driven configuration.

“Our goal with pPLL03 was to deliver best-in-class jitter performance with integration flexibility in advanced nodes like GlobalFoundries 22FDX,” said Julian Jenkins, CTO at Perceptia. “The silicon data validates our design and methodology, and the IP is production-ready.”

GlobalFoundries’s 22FDX platform is tailored for low-power, high-density applications such as mobile, edge AI, RF connectivity, and embedded processing. The availability of pPLL03 in this process gives customers a differentiated clocking solution optimised for FD-SOI characteristics.

The pPLL03 design kit includes:

- Liberty (.lib) timing models

- Verilog and Verilog-A simulation models

- GDSII and LEF physical views

- CDL netlist

- Integration guidelines and layout constraints

- Comprehensive verification and characterisation data

The kit is available immediately to qualified licensees.

For licensing inquiries or to request a technical brief, contact sales@perceptia.com or visit www.perceptia.com.

About pPLL03p

PLL03 is a compact, low-jitter phase-locked loop (PLL) IP core optimised for advanced process nodes. Delivering output clock frequencies up to 4GHz, pPLL03 is designed for use in a wide range of high-performance applications including high-performance computing, AI acceleration and timing-critical logic, it delivers superior jitter and integration flexibility. pPLL03 is especially suited for designs with many clock domains. pPLL03 enables designers to confidently implement advanced timing architectures without compromising on area or power.

About Perceptia Devices

Perceptia Devices is an IP and design services provider, based in Sydney, Australia. With a focus on PLLs and precision timing, Perceptia supports customers across a wide range of applications including wireless communications, AI/ML, data converters, IoT, and mixed-signal SoCs with high performance, low area PLLs.

For more information or to request the pPLL05 datasheet, please contact:

📧sales@perceptia.com

🌐www.perceptia.com

Related Semiconductor IP

- All Digital Fractional-N PLL for Performance Computing in GlobalFoundries 22FDX

- X-band (7.9 − 9.8GHz) High Performance Frac-N PLL

- Frac-N PLL on Samsung 28nm LN28FDS

- Frac-N PLL on Samsung 8nm LN08LPP

- Frac-N PLL on Samsung 4nm LN04LPP

Related News

- Perceptia Releases Design Kit for pPLL05 on GlobalFoundries 22FDX Platform

- Perceptia Announces Availability of Cryogenic 10-bit ADC and DAC IP in GF 22FDX

- Perceptia confirms performance of 11-GHz 0.4-ps 40-nm DSP-based PLL hard IP Core

- Perceptia Joins GlobalFoundries FDXcelerator Program to Bring PLL Technology to Portable Devices

Latest News

- EU DARE Project Is Scrambling to Replace Codasip

- Sofics and Alcyon Photonics Partner to Support Next-Generation Photonic Systems

- QuickLogic Appoints Quantum Leap Solutions as Authorized Sales Representative

- Cadence and NVIDIA Expand Partnership to Reinvent Engineering for the Age of AI and Accelerated Computing

- Cadence and Google Collaborate to Scale AI-Driven Chip Design with ChipStack AI Super Agent on Google Cloud