芯来科技正式推出Bus_Fab总线IP,助力高效芯内结构演进

2025-08-06 -- 在现代SoC设计中,总线互联(Bus Fabrication)系统作为数据与控制信号传输的核心枢纽,早已超越“连接器件”的基础角色,成为决定系统整体性能、资源调度效率与可扩展能力的关键模块。随着多核计算、AI加速、异构协同等技术快速演进,芯片内部的互联结构面临更高带宽、更低延迟与更强兼容性的挑战。

为满足新一代SoC对高效互联的需求,芯来科技正式推出自主研发的Bus_Fab(互联总线矩阵IP),具备高度可配置性、丰富仲裁策略与灵活组网能力,可广泛应用于MCU、AIoT、边缘计算、汽车电子等多样化系统平台中,是构建高效芯内通信结构的重要基础组件。

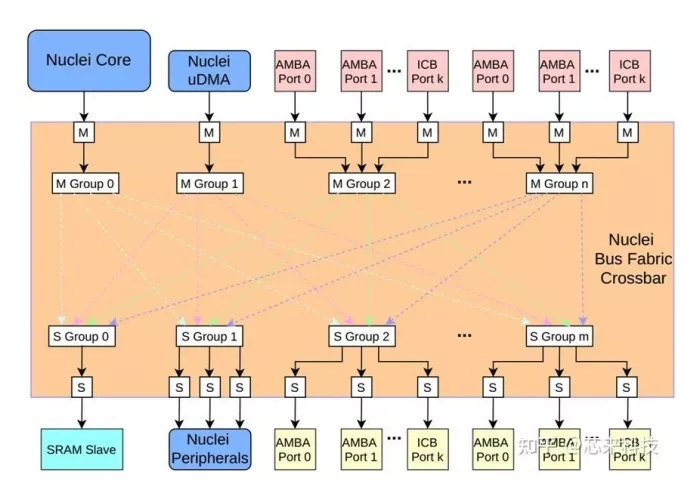

Bus_Fab是芯来科技开发的互联总线矩阵模块,支持AXI、AHB、APB或ICB总线。其中总线Master和Slave的个数可配置,每个Master和Slave的总线类型可配置,支持的总线仲裁有rrobin、priority、indic、indic_priority或rbin4类型,在BUS内部,多个Master和Slave按照Group组织,不同Group之间的访问,按照cross bar的优先级进行仲裁,同一个Group内部的多个Port访问,按照Group的内部优先级配置进行仲裁。

BUS模块框图

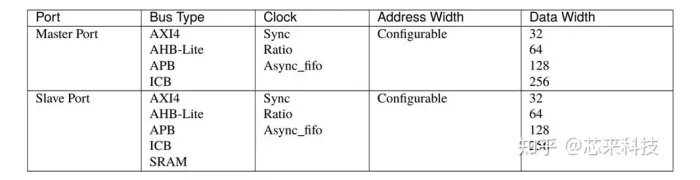

BUS总线的每个master和slave port支持的配置如下表所示:

BUS总线配置表

在SoC系统中,Bus_Fab不仅仅是数据流动的通道,更是连接CPU核心与各类外设、存储与加速单元之间的关键枢纽。它承载着系统中大量并发事务的数据交互与控制调度,其性能、灵活性与可靠性,直接决定了整个芯片平台的运行效率与扩展能力。对于构建具备实时响应、高吞吐、低功耗特性的RISC-V SoC平台,拥有一款稳定、高效且可定制的互联总线IP至关重要。

芯来科技此次推出的Bus_Fab,正是我们在“通用处理 + 系统互联”双路线布局中的重要一环。作为核心IP之一,它不仅为现有产品线提供了高效的数据互联支持,也为未来SoC子系统的模块化集成奠定了坚实基础。芯来科技的Bus_Fab支持单独授权,也可以以子系统方式授权给客户。

芯来科技将在现有Bus_Fab的基础上,持续推出更多面向高带宽传输、异构互联、片上网络(NoC)等需求的下一代总线/互联系统IP产品,进一步强化我们在RISC-V SoC平台中的系统级解决方案能力,赋能智能终端、汽车电子、边缘计算等更广泛应用场景。