DCD-SEMI推出多通道 DMA 控制器 IP 内核DDMA

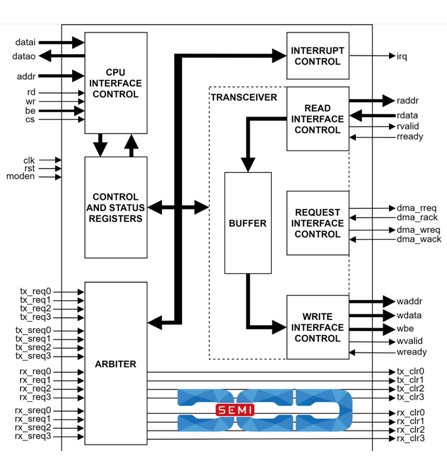

Bytom, Poland -- December 15, 2022 -- The DDMA is a four-channel Direct Memory Access Controller, with purpose to transfer data between memories and peripherals – to significantly reduce CPU utilization during data transfers. It can be programmed by any CPU via a 32-bit or 8-bit native interface.

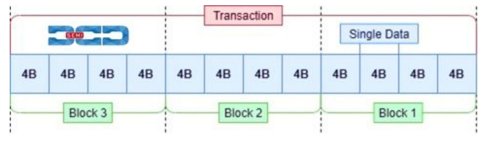

The DDMA can perform data transactions of configurable size over 32-bit address space. A single transaction size can be set in a range from 1B to 16MB. To limit the negative impact of different reads and writes timing the DDMA features transfer data buffer. This buffer is a 32-bit FIFO memory with configurable depth.

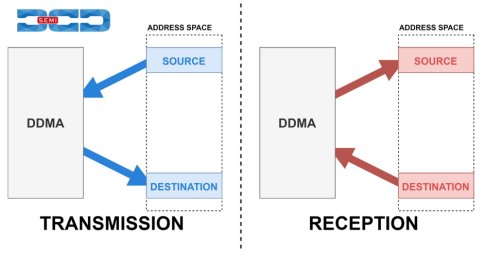

Data transactions can be triggered either by hardware or software. Hardware initialization is achieved via the Peripheral Request Interface, while software initialization is done by the CPU via registers. The Peripheral Request Interface is used by external controllers (peripherals) to set data transaction request on specific DDMA channel. Each of the DDMA channels has a set of Peripheral Request Interface signals associated with it. Peripherals can request the transmission or reception of data. When multiple channels await data transfer the arbitration process utilizes a round-robin algorithm.

DCD-SEMI’s IP Core includes four DDMA channels. Each has its configuration registers and enable bit. The DDMA offers three transfer modes:

- SINGLE - single data transfer on request,

- NORMAL - one data block transfer on request,

- BLOCK - all data blocks transfer on request.

They are distinguished by the amount of data transferred on a single request. Data transaction is divided into blocks. It is possible to configure the number of block bytes and number of blocks in a transaction. Data transfer is performed between the data source and the data destination. The DDMA channel can perform reads and writes on 32-bit, 16-bit, and 8-bit data which is separately configurable for both source and destination. Source and destination addresses can be freely configured.

The DDMA offers three addressing modes:

- INC – increment address after each data access,

- DEC – decrement address after each data access,

- FIXED – the address is fixed.

Apart from the above, the IP Core has three sources and destination address reload options:

- TRANSACTION – address is reloaded after the full transaction,

- BLOCK – the address is reloaded with each block transferred,

- NEVER – the address is never reloaded.

Address, block, and byte registers are double buffered so that if they are changed while the channel is busy, the change does not take effect until the current data transfer is over.

Each channel has status and transfers status flags. Channel status is defined as BUSY, PENDING, or IDLE. Transfer status flags inform about the amount of data that has been sent by the channel. Proper flags are set after the transmission of single data, block, or transaction. Each transfer status flag is masked which allows for generating an interrupt request when a specific data transfer situation occurs.

Key features :

- 32-bit or 8-bit internal registers access

- 32-bit transmission address range

- Transaction size from 1B up to 16MB

- Four transmission channels

- Round robin arbitration

- Data buffer with configurable size

- For each channel:

- Enable bit

- Software transmission request

- Peripheral request interface:

- Transmission request

- Single data transmission request

- Reception request

- Single data reception request

- Configurable request clear signal

- Transfer status flags:

- Transaction finished

- Block finished

- Single data finished

- Transfer status flags maskable interrupts

- Three transfer modes:

- SINGLE

- NORMAL

- BLOCK

- Independently configurable source and destination data width:

- 32-bits

- 16-bits

- 8-bits

- Configurable source and destination base addresses

- Three addressing modes: INC, DEC, FIXED

- Three source and destination address reload options each:

- TRANSACTION

- BLOCK

- NEVER

- Transaction divided into blocks

- Configurable transfer size: including amount of blocks and blocks size

- Double buffered address, block and byte registers

- Available DMA interface wrappers:

- Native 32-bit interface

- AMBA – APB / AHB / AXI Lite

- Software reset

- Configurable hardware reset

- Fully synthesizable

- No internal tri-states

Related Semiconductor IP

- DMA Controller

- DMA Controller

- Multi-Channel Streaming DMA Controller

- AHB/AXI/Wishbone DMA Controller

- ULL PCIe DMA Controller

Related News

- Digital Blocks通过在PCIe或UDP / IP网络接口上优化视频以及DMA数据流传输,扩展AMBA多通道DMA控制器IP内核系列的领军地位。

- T2M-IP发布MIPI D-PHY v2.5 Tx和DSI Tx控制器v1.2:针对高级SoC的硅验证、低功耗、经济高效的IP核心解决方案

- CAST 推出 I2C/SPI 控制器 IP 核,实现更加便捷的串行通信方式

- 面向高端汽车电子和消费类应用的CAN XL 控制器 IP 及完整安全套件可立即向客户授权!