Quad SPI Flash Memory Controller

The SPI-MEM-CTRL core is an SPI serial NOR and serial NAND flash memory controller, supporting Single, Dual and Quad I/O SPI acce…

Overview

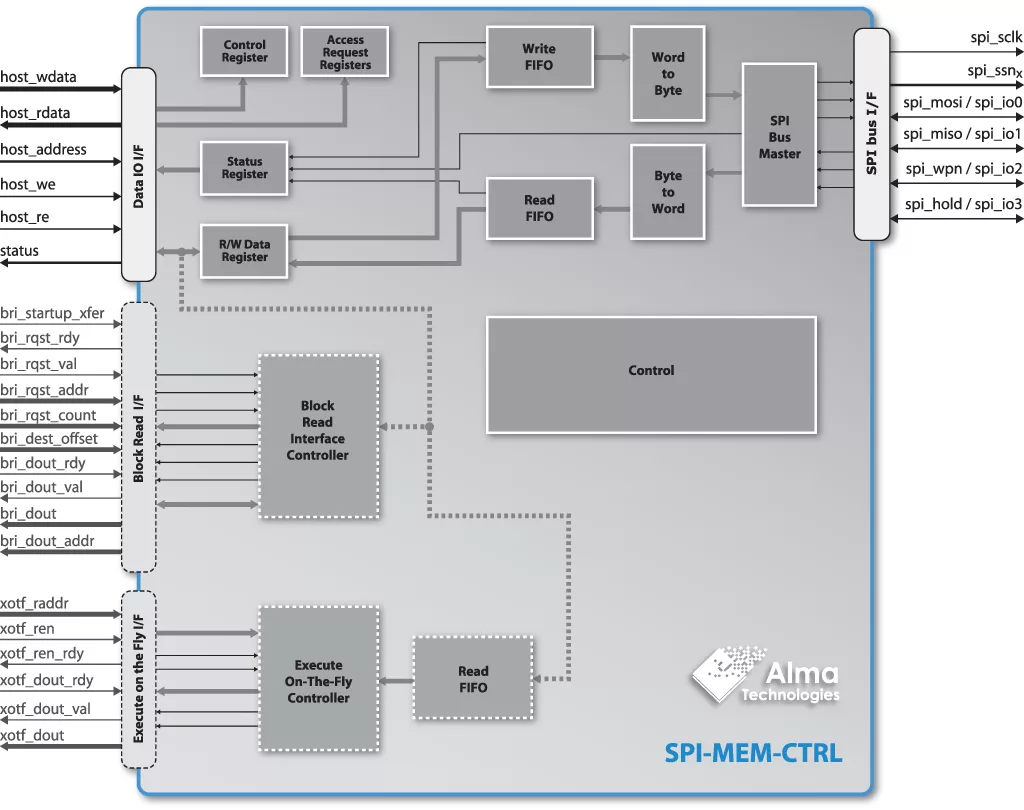

The SPI-MEM-CTRL core is an advanced SPI serial NOR and serial NAND flash memory controller, supporting Single, Dual and Quad I/O SPI accesses and including Boot and Execute on-the-fly features.

The SPI-MEM-CTRL core is designed to provide to a host a simple interface for controlling SPI Serial Flash Memories. The core is highly flexible and can be configured before synthesis or programmed during runtime to support a large number of SPI Serial Flash memories, even less standard ones.

A host can interface to the Serial Flash in a number of ways. Transferring data from the Flash memory to the host is done with minimum effort with a Block Read Interface, which uses a DMA mechanism to transfer a block of data to the host’s memory space. Alternatively, the host can introduce a read request using the core’s programmable registers. Then the core serves this request and sends the necessary instructions to the Serial Flash device. An additional RAM like interface which permits on-the-fly code execution is also available.

The SPI-MEM-CTRL controller has been rigorously verified. A complete verification environment that helps designers verify the functionality and compliance of the core, including additional aids for system-level simulation, are available.

Key features

- Device Independent:

- Supports serial NOR and serial NAND SPI flash memories

- Implements identification mechanism to detect connected serial flash memories

- Configurable memory features to allow support for more serial flash devices

- Efficient Bandwidth Utilization:

- Automatic identification of maximum bandwidth access mode among:

- single SPI

- dual output SPI

- dual I/O SPI

- quad I/O SPI

- Automatic identification of maximum bandwidth access mode among:

- Flexible Access Model:

- Registered mapped I/O

- NOR SPI Flash features:

- Read access sizes from 1 byte up to memory density

- Read accesses starting from any address offset

- Write access sizes from 4 bytes up to memory density

- Write accesses starting from any address offset that is 32-bit word aligned

- Erasure of:

- any sector (4KB)

- any block (64KB)

- whole chip

- NAND SPI Flash features:

- Read access sizes from 1 byte up to memory density

- Read accesses starting from any address offset that is 32-bit word aligned

- Write access sizes from 4 bytes up to memory density

- Write accesses starting from any address offset that is 32-bit word aligned

- Erasure of:

- any block (128KB)

- Ease of Integration:

- Auto-detection of a wide set of serial flash devices to minimize programming overhead

- Auto detection of the fastest way to read or program the memory, to maximize bandwidth and minimize programming overhead

- Deep Power-down Mode support to minimize power consumption

- Design Quality:

- Robust verification with integrated self-checking testbench environment

- Scan-ready design

Block Diagram

What’s Included?

- Clear-text RTL sources for ASIC designs, or pre-synthesized and verified Netlist for FPGA and SoC devices

- Release Notes, Design Specification and Integration Manual documents

- Bit Accurate Model (BAM) and test vector generation binaries, including sample scripts

- Pre-compiled RTL simulation model and gate-level simulation netlist for the FPGA Netlist license

- Self-checking testbench environment sources, including sample BAM generated test cases

- Simulation and sample Synthesis (for ASICs) or Place & Route (for FPGAs) scripts

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about SPI / QSPI XSPI IP core

Unleashing the Power of Communication: Exploring the XSPI Protocol and Arasan Chip Systems' XSPI IP Portfolio

Frequently asked questions about SPI / QSPI / xSPI IP cores

What is Quad SPI Flash Memory Controller?

Quad SPI Flash Memory Controller is a SPI / QSPI XSPI IP core from Alma Technologies listed on Semi IP Hub.

How should engineers evaluate this SPI / QSPI XSPI?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this SPI / QSPI XSPI IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.