audio voice DSP IP

Filter

Compare

27

IP

from

8

vendors

(1

-

10)

-

HiFi iQ DSP

- 8X Increased AI Performance: Run the entire voice AI networks efficiently with configurable AI-MAC

- 2X Increased Raw Compute Performance: Wider SIMD allows more computations

- Expanded Data Type Support: Efficiently run cutting-edge voice AI models in FP8, BF16, and more

-

Tensilica HiFi 4 DSP

- Support for eight 32x16-bit MACs per cycle under specific conditions

- Four very long instruction word (VLIW) slot architecture capable of issuing two 64-bit loads per cycle

- Optional vector floating-point unit available, providing up to four single-precision IEEE floating-point MACs per cycle

- Software compatibility with the complete HiFi DSP product line, totaling over 300 HiFi-optimized audio and voice codecs and audio enhancement software packages

-

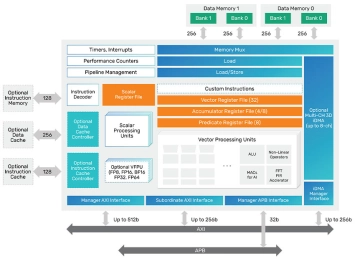

High performance dual-issue, out-of-order, 7-stage Vector processor (DSP) IP

- Design Flexibility

- Portability

- Ease of programmability

-

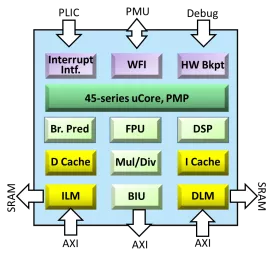

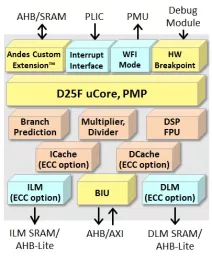

32-bit 8-stage superscalar processor that supports RISC-V specification, including GCNP (DSP)

- The 32-bit D45 is an 8-stage superscalar processor that supports RISC-V specification, including “G” (“IMAFD”) standard instructions, “C” 16-bit compression instructions, “P” Packed-SIMD/DSP instructions, “B” bit manipulation, and Andes performance enhancements, plus Andes Custom Extension™ (ACE) for user-defined instructions.

-

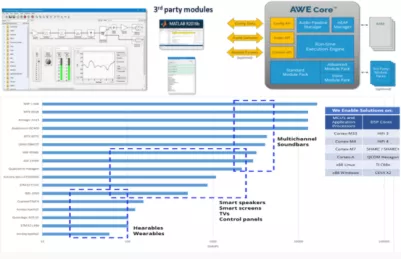

Audio Weaver - Audio Algorithm Generator tool (Design, Develop, Deploy)

- Integrate or Create advanced audio features

- Realtime Interface for design and debug

- Open APIs for external tools and scripting

- Includes Native Target with AWE Core for Windows

-

Compact High-Speed 32-bit CPU Core with DSP

- AndeStar™ V5 ISA, compliant to RISC-V technology

- DSP/SIMD ISA to boost the performance of digital signal processing

-

Tensilica HiFi 5 DSP

- Five very long instruction word (VLIW)-slot architecture capable of issuing two 128-bit loads per cycle

-

Compact neural network engine offering scalable performance (32, 64, or 128 MACs) at very low energy footprints

- Best-in-Class Energy

- Enables Compelling Use Cases and Advanced Concurrency

- Scalable IP for Various Workloads

-

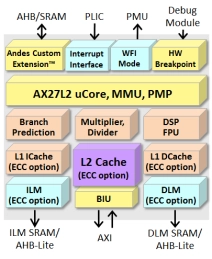

64-bit CPU Core with Level-2 Cache Controller

- AndeStar™ V5 Instruction Set Architecture (ISA), compliant to RISC-V technology

- Floating point extensions

- DSP/SIMD ISA to boost the performance of voice, audio, image and signal processing

- Andes extensions, architected for performance and functionality enhancements

- Separately licensable Andes Custom Extension™ (ACE) for customized acceleration