Compact neural network engine offering scalable performance (32, 64, or 128 MACs) at very low energy footprints

The Cadence® Tensilica® NNE 110 offers an energy-efficient hardware-based AI engine that can be paired with a Tensilica based DSP.

Overview

The product architecture natively supports the most common network layers found in these applications including convolution, depth-wise separable convolution, fully connected, LSTM, pooling, reshaping, and concatenation layers. Other layers can be supported (and further accelerated using TIE) using the host Tensilica DSP. The NNE 110 provides performance scalability from 32 to 128 MACs for 8x8-bit MAC computation, suiting a variety of low-power AI needs. It offers unique features for AI enhancement including hardware-based sparsity for compute and bandwidth reduction as well as on the-fly weight decompression for smaller system footprints.

Key features

- Best-in-Class Energy.

- High MAC utilization and sparsity acceleration deliver significant energy improvements over CPUs and DSPs.

- Enables Compelling Use Cases and Advanced Concurrency.

- Resource-intensive AI applications like advanced noise suppression and speech recognition can run concurrently with all other workload needs.

- Scalable IP for Various Workloads.

- Balance area and performance based on system and use case requirements.

- Small System Footprint.

- Compact design area and compression/decompression reduce system memory and bandwidth requirements.

- Fast Time to Market.

- Fully verified IP packages including comprehensive software solutions that leverage existing programming paradigms.

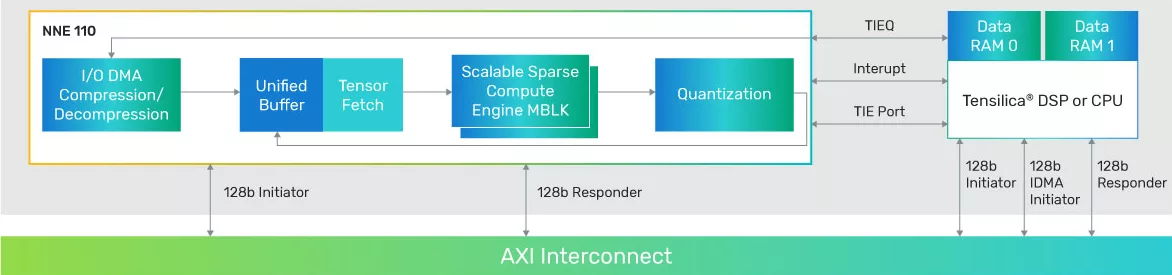

Block Diagram

Benefits

- Supported NNE MAC configurations: 32, 64, and 128 8-bit MACs (# of 16-bit MACs = 1/4th of # 8-bit MACs)

- Supported UBUF (local memory) configurations: 32kB, 64kB, 128kB and 256kB

- Bandwidth configurations: 32/16/8/4 bytes/clock and AXI bus of 128-bit width

- Clock rates up to 1GHz

- Runtime sparsity-based cycle speedup

- Runtime weight compression

- Asymmetric quantization support

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about Edge AI Accelerator IP core

Using edge AI processors to boost embedded AI performance

The Industry’s First USB4 Device IP Certification Will Speed Innovation and Edge AI Enablement

Accelerating Your Development: Simplify SoC I/O with a Single Multi-Protocol SerDes IP

IoT Was Interesting, But Follow the Money to AI Chips

Designing Energy-Efficient AI Accelerators for Data Centers and the Intelligent Edge

Frequently asked questions about Edge AI Accelerator IP cores

What is Compact neural network engine offering scalable performance (32, 64, or 128 MACs) at very low energy footprints?

Compact neural network engine offering scalable performance (32, 64, or 128 MACs) at very low energy footprints is a Edge AI Accelerator IP core from Cadence Design Systems, Inc. listed on Semi IP Hub.

How should engineers evaluate this Edge AI Accelerator?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Edge AI Accelerator IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.