Visual Processor IP

Filter

Compare

19

IP

from

9

vendors

(1

-

10)

-

Display Processor for VR

- Superior User Experiences on Mobile

- Efficiency and Bandwidth Savings

- Increased Performance, Same Footprint

-

PowerVR Series9XTP Graphic Processor

- Premium smartphone and pro tablet

- Augmented and virtual reality

- Automotive

-

PowerVR Series9XMP Graphic Processor

- Augmented & Virtual reality

- Automotive (ADAS)

- Smartphone & tablet

-

PowerVR Series9XEP Graphic Processor

- Augmented & Virtual reality

- Automotive (ADAS)

- Smartphone & tablet

-

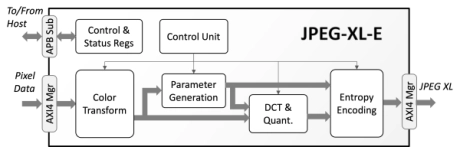

JPEG XL Encoder

- The JPEG-XL-E implements an image compression engine compliant to the JPEG XL, ISO/IEC 18181 standard.

- Leveraging the advanced coding tools of the JPEG XL standard, the core achieves substantially higher compression efficiency than legacy JPEG while requiring fewer hardware resources than JPEG 2000 and comparable codecs.

-

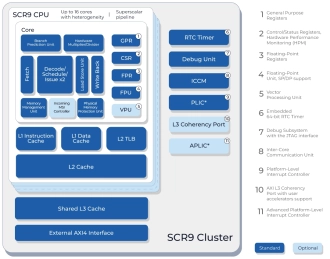

High-performance Linux-capable application core with a 12-stage dual-issue out-of-order pipeline, a VPU, cache coherency, and a hypervisor

- SCR9 is a high-performance, silicon-proven, Linux-capable 64-bit RISC-V processor core for entry-level server-class applications and personal computing devices.

- The SCR9 core supports RISC-V standard "I" Integer, "M" Integer Multiplication and Division, "A" Atomic, "C" 16-bit Compressed, "F" Single-Precision Floating-Point, "D" Double-Precision Floating-Point, "V" Vector Operations, "B" Bit Manipulation, and "K" Scalar Cryptography extensions.

-

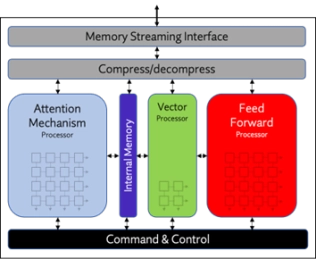

NPU IP Core for Edge

- Origin Evolution™ for Edge offers out-of-the-box compatibility with today's most popular LLM and CNN networks. Attention-based processing optimization and advanced memory management ensure optimal AI performance across a variety of networks and representations.

- Featuring a hardware and software co-designed architecture, Origin Evolution for Edge scales to 32 TFLOPS in a single core to address the most advanced edge inference needs.

-

SWD Verification IP

- Supports ARM Serial Wire Debug Interface specifications.

- Full SWD Host and Device functionality.

- Supports single bidirectional data connection and a separate clock to transfer data synchronously.

- Supports START and STOP bit generation and handling.

-

IP cores for ultra-low power AI-enabled devices

- Ultra-fast Response Time

- Zero-latency Switching

- Low Power