Ultra Ethernet IP

Filter

Compare

25

IP

from

15

vendors

(1

-

10)

-

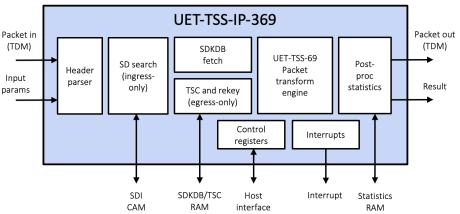

Multi-channel Ultra Ethernet TSS Complete Layer

- The UET-TSS-IP-369 (EIP-369) is an inline, high-performance, multi-channel packet engine that provides the complete TSS layer, bypass/drop and basic crypto processing at rates up to 1.6Tbps.

- The engine is designed for integration into the systems that require TSS processing for one or more ports. The engine is provided as separate ingress and egress data paths.

- The EIP-369 embeds the UET-TSS-IP-69 for the packet transformation.

-

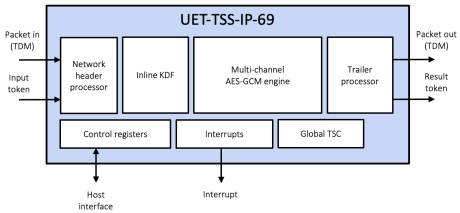

Multi-channel Ultra Ethernet TSS Transform Engine

- The UET-TSS-IP-69 (EIP-69) is a high-performance, multi-channel transform engine that provides the complete TSS packet transformation (including KDF and IP/UDP updates), bypass/drop and basic crypto processing at rates up to 1.6Tbps.

- The engine is designed for integration into the systems that require TSS processing for one or more ports. The engine is provided as separate ingress and egress data paths.

-

Verification IP for Ultra Ethernet (UEC)

- Native SystemVerilog/UVM

- Source code test suite including UNH-IOL (optional)

- Runs natively on major simulators

- Built-in protocol checks

- Verification plan and coverage

-

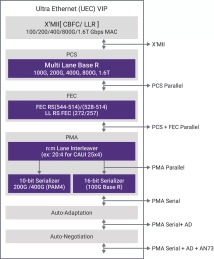

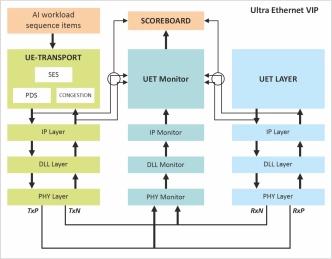

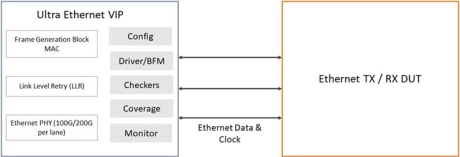

Ultra Ethernet Verification IP

- The Ultra Ethernet (UE) Verification IP provides an effective & efficient way to verify the components interfacing with Ethernet interface of an IP or SoC.

- The UE VIP is compliant with IEEE standard 802.3-2018 & UE Specifications V1.0.

- This VIP is light weight with easy plug-and-play interface so that there is no hit on the design cycle time.

-

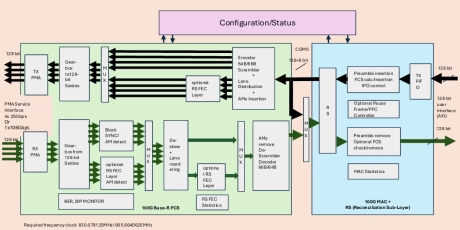

100G MAC/PCS Ultra Ethernet

- The IP integrates MAC Layer, RS Sub-Layer and 100G PCS Base-R cores according to IEEE 802.3 standard to provide seamless connection between an application and serdes interfaces

- 128-bit interface for TX and RX between MAC and the application Serdes interface – configurable to support PAM2 and PAM 4

-

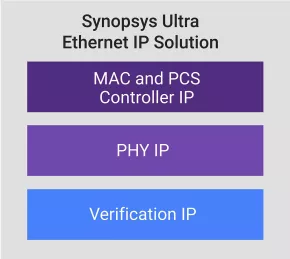

Complete 1.6T Ultra Ethernet IP Solution

- Ethernet MAC, PCS and PHY to complete a full Ultra Ethernet interface stack

- Supports evolving IEEE 802.3 and OIF-224G electrical standards

- Provides support for 4 x 400G, 2 x 800G, and 1.6T Ethernet rates using 112Gbps and 224Gbps SerDes

- Meets performance criteria for chip-to-chip, chip-to-module, and long reach copper/backplane interconnects

-

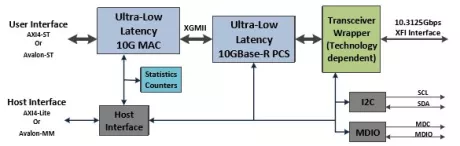

10G Ultra Low Latency Ethernet Solution

- Ultra low latency MAC; Tx = 12.4ns , Rx = 15.5ns; (32-bit user interface mode)

- Ultra low latency 10GBase-R PCS; Tx = 12.4ns, Rx = 12.4ns

-

25G Ultra Low latency, 64-bit Ethernet MAC + PCS Solution (64-bit and 128-bit UI)

- MAC Core Features

- PCS Core Features

-

Simulation VIP for Ethernet UEC

- Support testbench language interfaces for SystemVerilog, UVM, OVM, e, and SystemC

- Callbacks access at multiple TX and RX queue points for scoreboarding, data manipulation, and error injection

- Transaction Tracker: Configurable tracking of all the transactions on the channels

-

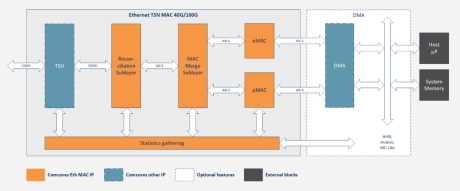

Ethernet TSN MAC 40G/100G

- Silicon agnostic Ethernet TSN MAC IP with speeds of 40G and 100G, based IEEE 802.3 Ethernet Layer 2 solution with support for key TSN features