Serial NOR Flash IP

Filter

Compare

11

IP

from

7

vendors

(1

-

10)

-

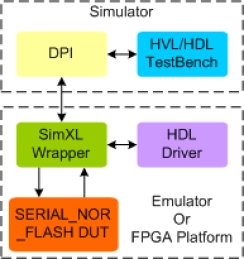

Serial NOR Flash Synthesizable Transactor

- Supports 100% of Serial NOR Flash protocol standard

- Supports all the Serial NOR Flash commands as per the specs

- Supports single and double transfer rate (STR/DTR)

- Supports following protocols in both STR and DTR:

-

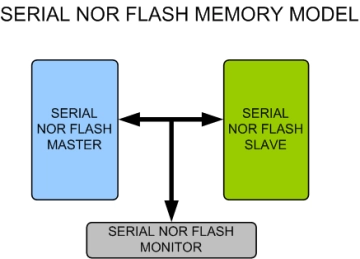

Serial NOR Flash Memory Model

- Supports Serial NOR Flash memory devices like MT25QL128ABA, MT25QL512ABA, MX25L12835F, MX25L25635F, N25Q032A from all leading vendors like Macronix, Micron, Winbond and many more.

- Supports 100% of Serial NOR Flash protocol.

- Supports all the Serial NOR Flash commands as per the specs.

- Supports Single and Double Transfer Rate (STR/DTR).

-

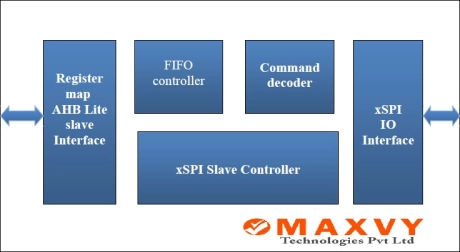

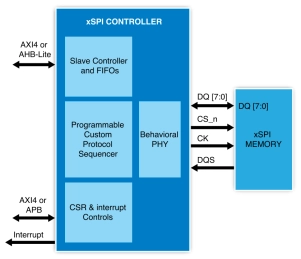

Expanded Serial Peripheral Interface (xSPI) Slave Controller

- The JESD251 Expanded Serial Peripheral Interface Slave controller is provides high data throughput, low signal count, and limited backward compatibility with legacy Serial Peripheral Interface(SPI) devices

- It is used to connect xSPI Master devices in computing, automotive, Internet of Things, Embedded system and mobile system processor to non-volatile memories, graphics peripherals, networking peripherals,FPGAs, sensors devices

-

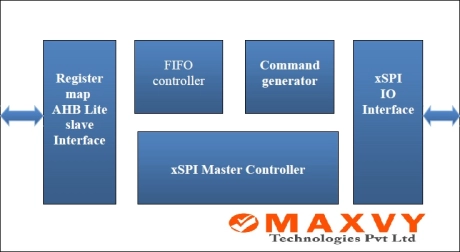

Expanded Serial Peripheral Interface (xSPI)Master Controller

- The Expanded Serial Peripheral Interface (JESD251) Master controller is low signal count, high data bandwidth, primarily for use in computing, automotive, Internet of Things, Embedded system and mobile system processor to connect multiple source of Serial Peripheral Interface (xSPI) slave devices like non-volatile memories, graphics peripherals, networking peripherals,FPGAs, sensors devices

-

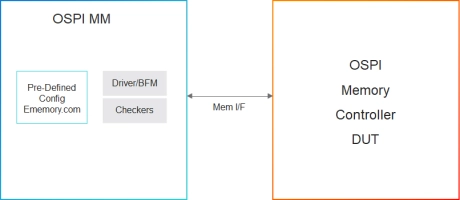

Simulation VIP for OSPI NOR

- Device Density

- From 256Mb to 2Gb, with frequency up to 133MHz in SPI and 200MHz in OSPI mode

- Operation Mode

- Extended SPI mode, Octal SDR and DDR mode (Single I/O and Octal I/O)

-

xSPI NOR/NAND Flash & HyperRAM Controller

- Memory mapped access to the connected flash devices

- Continuous Burst transfer support

- Auto boot support

-

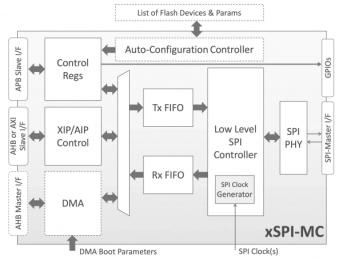

xSPI, HyperBus™, and Xccela™ Serial Memory Controller

- The xSPI-MC core is a versatile serial/SPI memory controller, which allows a system to easily detect and access the attached memory device or directly boot from it.

- The controller core supports most of the proprietary SPI protocols used by Flash and PSRAM device vendors and is compatible to JEDEC’s eXpanded SPI (xSPI), HyperBus™ and Xccela™ standards.

-

-

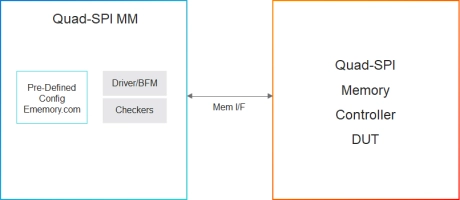

Simulation VIP for Q-SPI

- Device Density

- From 256Mb to 2Gb with frequency up to 166MHz

- Operation Mode

- Single I/O, Dual I/O, and Quad I/O (Q-SPI and QSPI) with single and double transfer rate (STR and DTR)

-

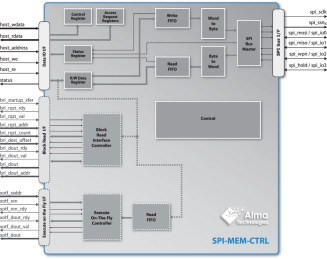

PSRAM Memory Controller IP

- DFSPI – SPI FLASH Controller with Execute in place – XIP (SINGLE, DUAL and QUAD SPI Bus Controller with DDR / DTR support and optional AES Encryption) + … NOR & NAND Flash Memory Support