Reed Solomon IP

Filter

Compare

49

IP

from

19

vendors

(1

-

10)

-

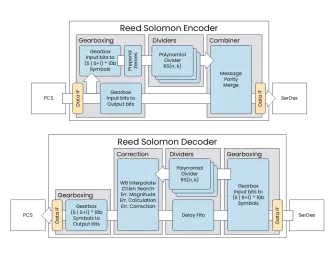

Reed Solomon II Intel® FPGA IP Core

- The Reed Solomon II Intel® FPGA intellectual property (IP) core offers a fully parameterizable Reed Solomon encoder and decoder

- These encoders and decoders are widely used for error detection and correction in a wide range of digital signal processing (DSP) applications for storage, retrieval, and transmission of data

- The Reed Solomon II Intel FPGA IP core is designed to support optical transport network (OTN) applications.

-

High-Speed Reed Solomon Intel® FPGA IP Core

- The High-Speed Reed Solomon Intel® FPGA intellectual property (IP) core uses a large parallel architecture to achieve a large throughput for applications that require 100 Gbps

- The IP core is suitable for 10G (such as OTN) or 100G Ethernet (IEEE 802.3bj/bm) applications.

-

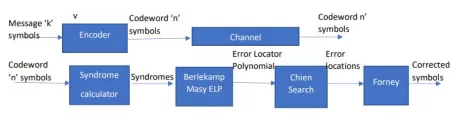

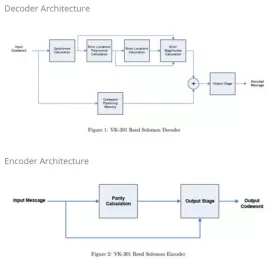

Reed Solomon Encoder and Decoder

- The Reed Solomon Encoder is fed with an input message of K information symbols, the Encoder appends 2T parity symbols to the input message in order to form the encoded codeword.

- The Reed Solomon Decoder receives an (N=K+2T) codeword, and it can locate and correct up to 8 possible symbol errors or up to 14 erasures.

- Both of the Encoder and the Decoder support any input timing pattern, in case of the Encoder; the output timing pattern will be the same as the input.

-

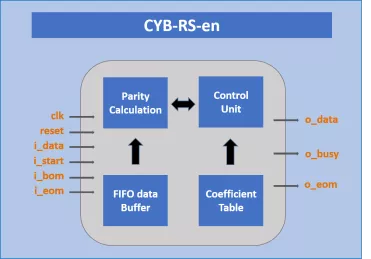

Reed Solomon FEC

- Designed to support any Reed Solomon code.

- Custom tailored to support specific codes see standard table below

- Low Latency

- FEC Processing cycles optimized for reduced buffering

-

Reed Solomon Error Correcting Code ECC

- Asynchronous operation

- No clocks required.

- No storage like memories SRAMS/ROMS/FilipFlops used

- No iterative Feedback in the pipeline

-

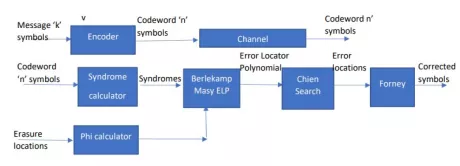

Reed Solomon Erasure Code

- Asynchronous operation

- No clocks required.

- No storage like memories SRAMS/ROMS/FilipFlops used

- No iterative Feedback in the pipeline

-

Reed Solomon Encoder

- Parameterizable bits per symbol

- Programmable codeword length

- Programmable number of errors

-

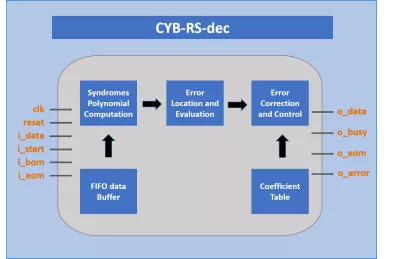

Reed Solomon Decoder

- Parameterizable bits per symbol

- Programmable codeword length

- Programmable number of errors

-

Reed Solomon

- High-performance Reed Solomon IP Core (Encoder and Decoder)

- Supports error and erasure decoding

- Parameterized codeword length

- Code generator polynomial: (x + ?0)(x + ?1)(x + ?2) . . . (x + ?15)

-

Clause 91 Reed Solomon FEC

- BASE-TX Core Features

- BASE-RX Core Features

- 25G-TX Core Features

- 25G-RX Core Features