Precise ITC IP

Filter

Compare

1,158

IP

from

53

vendors

(1

-

10)

-

Voltage Detect Vdet=2.5V Vhys=0.1V, generate a high/low level logic for a precise power supply monitoring system; UMC 90nm SP/RVT LowK Logic Process

-

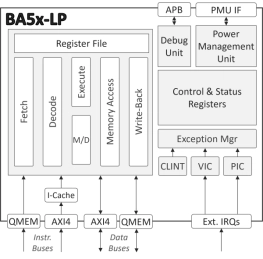

Low-Power Embedded RISC-V Processor

- The BA5x-LP is a highly efficient, low-power, 32-bit, deeply embedded processor IP core.

- The two-stage pipeline processor implements either the RV32I or RV32E instruction set.

- It comes pre-configured with the Multiply/Divide (M) and Compressed Instruction (C) extensions, providing a more flexible and capable platform without a significant increase in area or power.

-

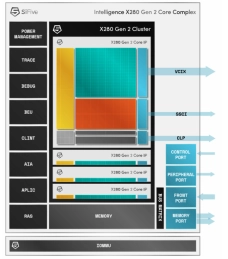

Multi-core capable RISC-V processor with vector extensions

- The SiFive® Intelligence™ X280 Gen 2 is an 8-stage dual issue, in-order, superscalar design with wide vector processing (512 bit VLEN/256-bit DLEN).

- It supports RISC-V Vectors v1.0 (RVV 1.0) and SiFive Intelligence Extensions to accelerate critical AI/ML operations.

-

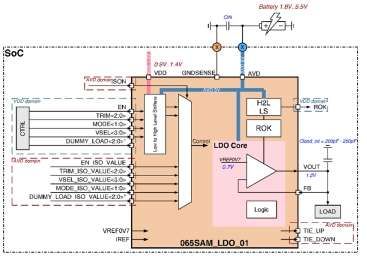

50 mA LDO voltage regulator (output voltage 0.9V/1.2V/1.34V) on Samsung 65nm

- 065SAM_LDO_01 is a low drop out voltage regulator designed to supply integrated circuits with stable and precise voltage.

- The LDO inputs voltage AVD from 1.8V to 5.5V and converts this voltage into a voltage VOUT 0.9V/1.2V/1.35V with 50mA load capacity.

- A Regulation OK (ROK) signal inform the system that LDO has completed its booting sequence and if its output is maintaining regulation for the current drawn by the load.

-

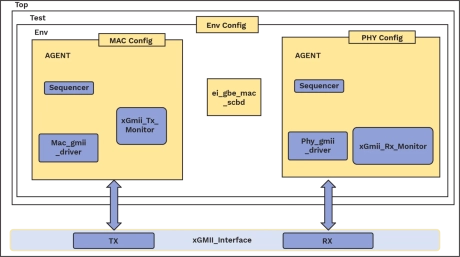

100G Ethernet Verification IP

- The 100G Ethernet Verification IP (VIP) offers a robust and high-performance solution for validating the critical MAC-to-PCS datapath in 100 Gigabit Ethernet systems.

- Designed to ensure protocol compliance, the VIP facilitates the generation, transmission, reception, and monitoring of various Ethernet MAC frame types, all while adhering to IEEE 802.3ba and related standards.

- Whether you are working on IP, subsystem, or SoC-level verification, this VIP is your go-to solution for comprehensive Ethernet testing.

-

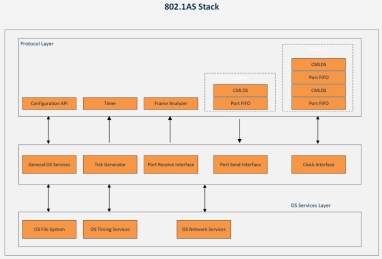

IEEE 802.1AS Software Stack

- The IEEE 802.1AS software stack implements the Timing and Synchronization protocol for time-sensitive applications over bridged and wireless networks.

- Based on a profile of the Precision Time Protocol (PTP) as defined in IEEE 1588, 802.1AS provides precise synchronization of clocks across all network devices, enabling accurate time distribution for Time-Sensitive Networking (TSN) and other real-time applications.

-

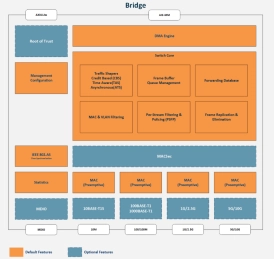

Bridge

- A complete integrated hardware and software solution that includes a TSN-capable Ethernet switch, a DMA engine, an IEEE 802.1 AS Time Synchronization system, and a Root of Trust security module.

-

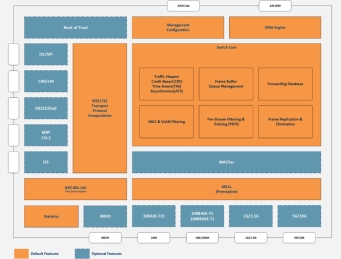

Zonal Controller

- Complete solution that integrates both hardware and software components including a TSN-capable Ethernet switch, a Root of Trust security module, and a transport protocol encapsulation system based on IEEE 1722

-

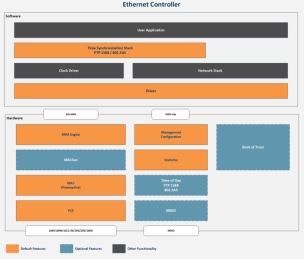

Ethernet Controller

- The Ethernet Controller is an ASIC proven high-performance, feature-rich network interface solution designed to deliver reliable, low-latency Ethernet connectivity across a broad range of embedded and enterprise applications.

- Comcores offers controllers ranging from 10M to 800G enabling seamless integration into systems requiring Ethernet connectivity.

-

SENT Protocol IP Core for Automotive Communication

- The DSENT, a hardware implementation of the Single Edge Nibble Transmission (SENT) protocol controller.

- Designed to comply with the SAE-J2716 standard, DSENT delivers a robust, low-cost solution for reliable data communication between automotive sensors and central units such as Engine Control Units (ECUs).