PCIe Gen 3.1 IP

Filter

Compare

6

IP

from

5

vendors

(1

-

6)

-

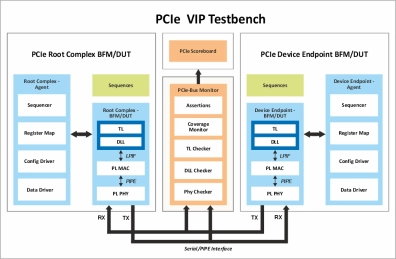

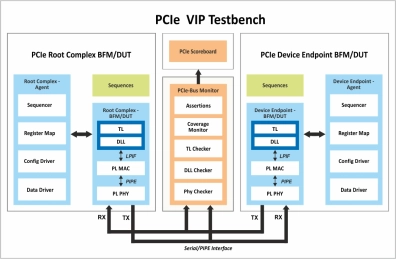

PCIe Gen 7 Verification IP

- The PCIe Gen 7 Verification IP provides an effective & efficient way to verify the components interfacing with PCIe Gen 7 interface of an IP or SoC.

- The PCIe Gen 7 VIP is fully compliant with latest PCI Express Gen 7 specifications. This VIP is a light weight with an easy plug-and-play interface so that there is no hit on the design cycle time.

-

PCIe Gen 6 Verification IP

- Compliant with PCI Express Specifications 6.1 (64GT/s), 5.0 (32GT/s), 4.0 (16GT/s), 3.1 (8GT/s), 2.0 (5GT/s) and 1.1 (2.5GT/s).

- Support for 64.0 GT/s Data Rate per lane with backwards compatible.

- Support for new PAM4 Signalling and Gray Coding.

- Support for both Flit Mode & Non-Flit Mode.

-

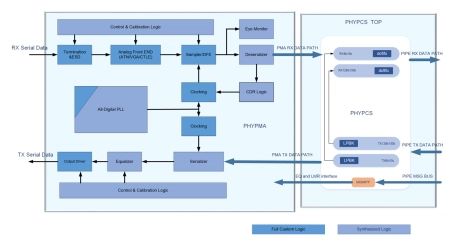

PCIe 3.1 Serdes PHY IP, Silicon Proven in TSMC 40LP

- Support PHY interface (PIPE4.3) enables multiple IP sources for USB3 MAC layer

- Supports 5.0Gbps and 10Gbps serial data transmission rate Supports 16-bit or 32-bit parallel interface Data and clock recovery from serial stream

- Support 8b/10b encoder/decoder(5Gbps), 128/130 encoder/decoder(BGbps) and error indication

- Tunable receiver detection to detect worse case cables

-

PCI Express Gen 4 PHY

- Support 16GT 8GT 5GT 2.5GT data rate

- Compliant with PCI Express 4.0, 3.1, 2.1, 1.1 and PIPE 4.2 standards

- x1, x2, x4, x8, x16 lane configuration with bifurcation

- Multi-tap adaptive programmable continuous time linear equalizer (CTLE) and decision feedback equalizer (DFE)

-

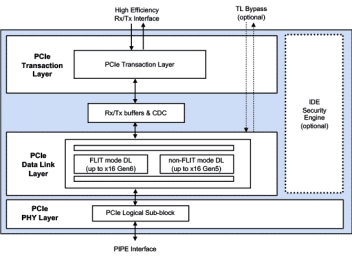

PCIe Gen 6 controller IP

- Designed to the latest PCI Express 6.0 (64 GT/s), 5.0 (32 GT/s), 4.0 (16 GT/s), 3.1/3.0 (8 GT/s), and PIPE 6.x (8, 16, 32, 64 and 128-bit) specifications

- Supports SerDes Architecture PIPE 10b/20b/40b/80b width

- Supports original PIPE 8b/16b/32b/64b/128b width

-

Multi-Rate Serdes IP Solution

- YouPHY-Serdes provides 2.5-32Gbps multi-rate SERDES IP which is designed for smooth integration of Multiple SERDES lanes demonstrate good performance class performance, area and power.

- The programmable PHY supports major standards such as PCIe Gen 4.0/3.0/2.0/1.0, USB 3.1/3.0, XAUI, SATA Gen 3.0/2.0/1.0, CEI-11G-LR, 10GBase-KX4, JESD204B, SGMII/QSGMII, RAPID I/O, HSSTP (Trace Port), V-By-One, DisplayPort and HMC.