PCIe 8.0 IP

Filter

Compare

72

IP

from

20

vendors

(1

-

10)

-

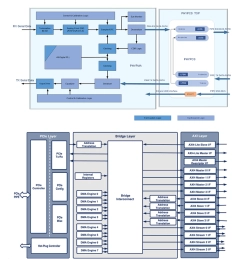

PCIe PHY and controller solution

- Brite 16Gbps PCIe PHY and controller solution provide high efficient interconnection that is optimized for PPA performance. The System can support short-reach or long-reach channels for plenty application scenarios.

- Brite PCIe controller to AXI architecture provides a high-performance, easy-to-use interconnect solution between PCI Express and the latest version of the AXI protocol. It inherits the leading architecture and features an AXI user interface with built-in DMA, compliant with the AMBA® AXI3 and AXI4 specifications.

-

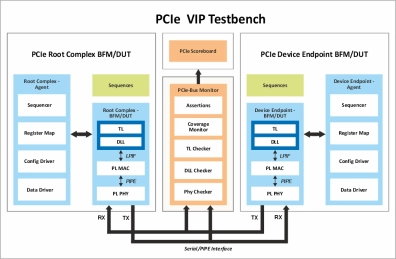

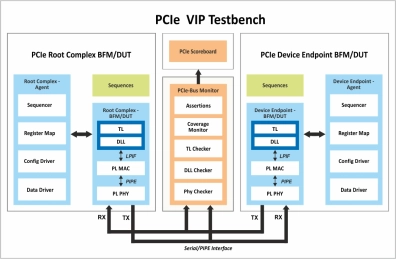

PCIe Gen 7 Verification IP

- The PCIe Gen 7 Verification IP provides an effective & efficient way to verify the components interfacing with PCIe Gen 7 interface of an IP or SoC.

- The PCIe Gen 7 VIP is fully compliant with latest PCI Express Gen 7 specifications. This VIP is a light weight with an easy plug-and-play interface so that there is no hit on the design cycle time.

-

PCIe Gen 6 Verification IP

- Compliant with PCI Express Specifications 6.1 (64GT/s), 5.0 (32GT/s), 4.0 (16GT/s), 3.1 (8GT/s), 2.0 (5GT/s) and 1.1 (2.5GT/s).

- Support for 64.0 GT/s Data Rate per lane with backwards compatible.

- Support for new PAM4 Signalling and Gray Coding.

- Support for both Flit Mode & Non-Flit Mode.

-

PCIe Gen 5 Verification IP

- Support for 32.0 GT/s Data Rate per lane with backwards compatible.

- Optimizing the Link to skip equalization at lower Data Rates when supporting 32.0 GT/s(optional feature).

- Lower pin count in pipe interface when supporting 32.0 GT/s.

- Support for newly added phy serdes architecture in pipe specification 5.0 .

-

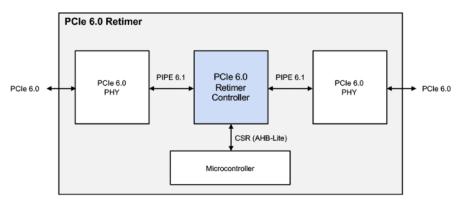

PCIe 6.0 Retimer Controller with CXL Support

- Designed to the latest PCI Express 6.0 (64 GT/s), and capable of supporting 32.0, 16.0, 8.0, 5.0 and 2.5 GT/s link rates

- Supports x1, x2, x4, x8 and x16 link widths

- CXL aware and supports sync header bypass

- Supports PIPE 5.2/6.1 compatible PHYs

- Optimized data-path for low latency insertion

-

PCIe 6.0 / CXL 3.0 PHY & Controller

- Innosilicon’s PCIe 6.0 and CXL 3.0 IP solutions combine high-performance controllers and PHYs, fully compliant with PCIe 6.0, CXL 3.0, and PIPE specifications

- These solutions deliver exceptional performance, low latency, power efficiency, and unparalleled flexibility, making them ideal for enterprise computing, data centers, cloud servers, AI and machine learning, storage expansion, and high-speed interconnect applications

-

PCIe 7.0 Controller (can be configured to support EP, RP, DM, or SW applications)

- Supports all required features of the PCI Express 7.0, 6.x, 5.0, 4.0, 3.1, 2.1, and 1.1 specifications

-

Configurable controllers for PCIe 4.0 and CCIX supporting Dual Mode applications

- Available in all port types including: Endpoint, Embedded Endpoint, Root Complex, Switch Port, Bridge, Dual Mode (Endpoint/Root Complex), and Multi-Port Switch

- Full Transaction Layer, Data Link Layer and Physical Layer

- Supports up to sixteen 64.0, 32.0, 16.0, 8.0, 5.0, 2.5 GT/s lanes

- Available in 32-, 64-, 128-, 256-, 512- or 1024-bit datapath widths for maximum flexibility

-

Automotive-grade controllers for PCIe 2.0/1.0 supporting Endpoint, Root Complex, Switch Port, and Dual Mode applications

- Available in all port types including: Endpoint, Embedded Endpoint, Root Complex, Switch Port, Bridge, Dual Mode (Endpoint/Root Complex), and Multi-Port Switch

- Full Transaction Layer, Data Link Layer and Physical Layer

- Supports up to sixteen 64.0, 32.0, 16.0, 8.0, 5.0, 2.5 GT/s lanes

- Available in 32-, 64-, 128-, 256-, 512- or 1024-bit datapath widths for maximum flexibility

-

Configurable controllers for PCIe 6.0 supporting Endpoint, Root Complex, Switch Port, and Dual Mode applications

- Available in all port types including: Endpoint, Embedded Endpoint, Root Complex, Switch Port, Bridge, Dual Mode (Endpoint/Root Complex), and Multi-Port Switch

- Full Transaction Layer, Data Link Layer and Physical Layer

- Supports up to sixteen 64.0, 32.0, 16.0, 8.0, 5.0, 2.5 GT/s lanes

- Available in 32-, 64-, 128-, 256-, 512- or 1024-bit datapath widths for maximum flexibility