PCIe Clock PHY IP

Filter

Compare

284

IP

from

22

vendors

(1

-

10)

-

PCIe PHY and controller solution

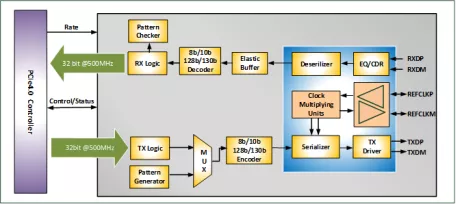

- Brite 16Gbps PCIe PHY and controller solution provide high efficient interconnection that is optimized for PPA performance. The System can support short-reach or long-reach channels for plenty application scenarios.

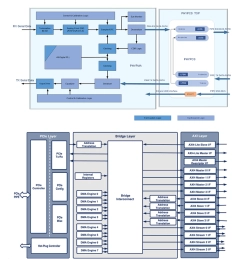

- Brite PCIe controller to AXI architecture provides a high-performance, easy-to-use interconnect solution between PCI Express and the latest version of the AXI protocol. It inherits the leading architecture and features an AXI user interface with built-in DMA, compliant with the AMBA® AXI3 and AXI4 specifications.

-

PCIe PHY

- Support for PCIe3(8.0Gbps),Backward compatible with 2.5Gbps and 5Gbps for PCIe

- Full compatible with PIPE4.2 interface specification

- Support 16bit and 32bit parallel data bus

- Independent channel power down control

- Supported reference clock input range from 25M to 400M

-

PCIe GEN6 PHY IP

- The PCIe GEN6 PHY IP achieves data rates up to 64GT/s per lane with PAM4 signaling thereby delivering reliable performance for high-speed data transfer.

- It supports advanced applications, including AI/ML, High-Performance Computing, and next-generation storage solutions.

-

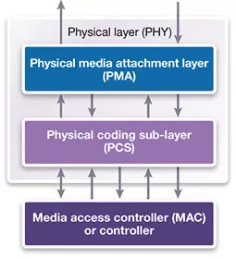

10G PHY for PCIe 3.0, TSMC N5 X1, North/South (vertical) poly orientation

- Supports 1.25 Gbps to 10 Gbps data rates

- Supports PCI Express 3.1, SATA 6G, SGMII

- Supports x1 to x16 macro configurations

-

10G PHY for PCIe 3.0, TSMC 16FFPLL x8, North/South (vertical) poly orientation

- Supports 1.25 Gbps to 10 Gbps data rates

- Supports PCI Express 3.1, SATA 6G, SGMII

- Supports x1 to x16 macro configurations

-

10G PHY for PCIe 3.0, TSMC 16FFPLL x4, North/South (vertical) poly orientation

- Supports 1.25 Gbps to 10 Gbps data rates

- Supports PCI Express 3.1, SATA 6G, SGMII

- Supports x1 to x16 macro configurations

-

10G MP PHY for PCIe 3.0/USXGMII/SGMII, TSMC 12FFC x1, North/South (vertical) poly orientation

- Supports 1.25 Gbps to 10 Gbps data rates

- Supports PCI Express 3.1, SATA 6G, SGMII

- Supports x1 to x16 macro configurations

-

10G PHY for PCIe 3.0, SS SF5 x2, North/South (vertical) poly orientation

- Supports 1.25 Gbps to 10 Gbps data rates

- Supports PCI Express 3.1, SATA 6G, SGMII

- Supports x1 to x16 macro configurations

-

10G PHY for PCIe 3.0, SS SF5 x1, North/South (vertical) poly orientation

- Supports 1.25 Gbps to 10 Gbps data rates

- Supports PCI Express 3.1, SATA 6G, SGMII

- Supports x1 to x16 macro configurations

-

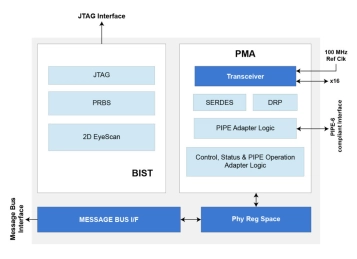

PCIe Gen4 PHY, x1-lane, RC/EP, TSMC 16FFC, N/S orientation

- Fully compliant with PCI Express Base 4.0, PCI Express Base 3.1, PCI Express Base 2.1 and PCI Express Base 1.1 electrical specifications

- Compliant with PIPE4.4.1 (PCIe) specification

- Supports all power saving modes (P0, P0s, P1, P2) defined in PIPE4.4.1 specification

- Supports L1 PM Substates with CLKREQ#