Octal SPI IP

Filter

Compare

35

IP

from

11

vendors

(1

-

10)

-

Octal SPI Master/Slave Controller

- Implements a controller for a single-, dual-, quad-, or octal-lane Serial Peripheral Interface (SPI) bus, which can operate either as a master or as a slave.

- Designed to work with a wide variety of SPI bus variants, the core supports run-time control of several SPI protocol parameters.

-

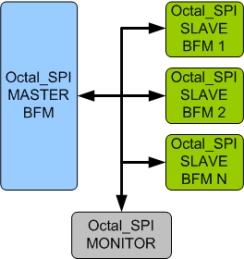

Octal SPI (Serial Peripheral Interface) Verification IP

- Follows Octal SPI basic specification as defined in Macronix (CMOS MXSMIO®(SERIAL MULTI I/O) Flash memory).

- Supports Master and Slave Mode.

- Supports Serial Peripheral Interface -- Mode 0

- Supports below Protocol modes

-

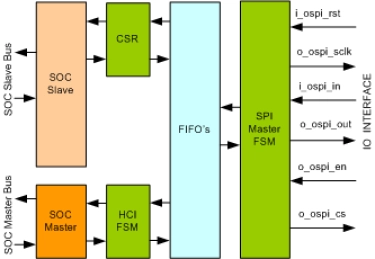

Octal SPI Master IIP

- Full Octal SPI Master Functionality

- Fast frequency support(Up to 133MHz)

- Compliant to the SPI de-facto standard

- Single, dual, quad and octal serial data lines

-

Octal SPI Controller – XIP functionality (SINGLE, DUAL, QUAD and OCTAL SPI Bus Controller with Double Data Rate support) and DMA Support

- Full Octal SPI Master Functionality

- Fast frequency support (Up to 133MHz)

- Compliant to the SPI de-facto standard

- Single, dual, quad, and octal serial data lines

-

FSPI Controller – XIP functionality (SINGLE, DUAL, QUAD and OCTAL SPI Bus Controller with Double Data Rate support)

- Set of software accessible control registers to

- execute any Flash memory command

- Support for most popular SPI like FLASH memories and PSRAM

- Supports any device clock frequency, polarity and phase

-

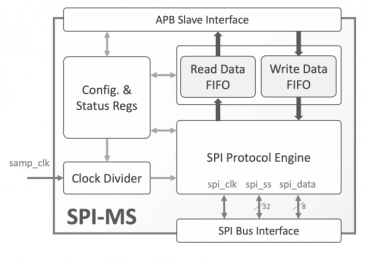

Serial Peripheral Interface - Master/Slave with single, dual, quad and octal SPI Bus support

- Operates with 8, 16 and 32 bit CPUs

- Full duplex synchronous serial data transfer

- DMA support

-

Octal SPI Controller

- The Octa SPI Controller and PHY IP supports the fastest access frequency of 200MHz, with DDR Mode and Double Transfer Rate (DTR) Protocol enabling data transfer rates up to 400Mbps with reduced read latency, including support for Octal DDR protocol with DQS for Octal SPI devices.

-

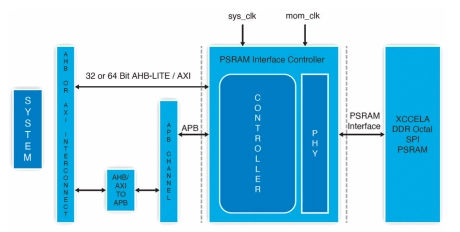

Octal SPI DDR PSRAM controller

- This controller supports AP Memory’s Xccela open standard Bus for digital interconnect and data communications, suitable for non-volatile and volatile memories such as PSRAM.

- This controller enables smooth integration AP memory’s of Xccela PSRAM memory chips into various new-gen devices made with mobile and wearable low power SoCs’.

- This memory controller implementation is designed to give the user full flexibility for driving the memory control signals and timing adjustment for data sampling.

-

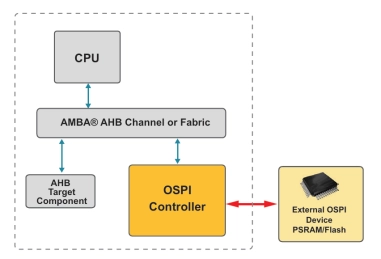

AHB Octal SPI Controller with PSRAM and XIP Support

- The Octal SPI Memory Controller IP core is a serial peripheral interface (SPI) master which controls an external serial device, usually an industry-standard FLASH or PSRAM memory device.

- In Software Mode, an AHB Master may access the register interface of the Controller to implement a wide range of protocol variants and/or commands on the SPI bus.

-

Host controller IP for controlling flash and other devices on the SPI bus: Quad SPI, Octal SPI, and xSPI

- Flexibility: Multiple SPI protocol support within single IP

- Simplicity: PHY-less IoT operation, or soft storage combo PHY IP simplifies SoC timing

- High Performance: Supports maximum Quad SPI / Octal SPI data rates and XIP (Execute In Place)