OPENEDGES IP

Filter

Compare

15

IP

from

1

vendors

(1

-

10)

-

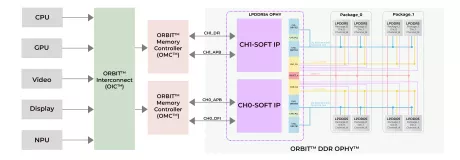

LPDDR5X/5/4X/4 combo PHY at 12nm

- Compliant with JEDEC JESD209-5C for LPDDR5x/5/4x/4 with PHY standards

- Delivering up to 8533Mbps

- DFI 5.1 specification PHY Interface Compliant

- Support up to 4 ranks

- Multiple frequency states

-

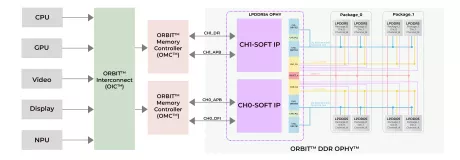

LPDDR5X/5/4X/4 PHY for 16nm

- Compliant with JEDEC standards for LPDDR5X/5/4X/4 with PHY standards

- DFI 5.0 Interface Compliant

- Supports up to 4 ranks

- Multiple frequency states

-

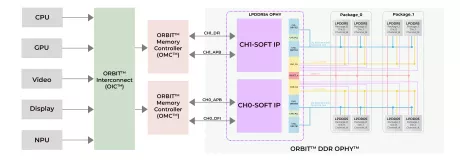

LPDDR5X/5/4X/4 combo PHY at Samsung SF5A

- Compliant for JEDEC standards for LPDDR5X/5/4X/4 with PHY standards

- DFI 5.1 specification PHY Interface Compliant

- Support up to 4 ranks

- x16 and x32 channel support

-

LPDDR5X/5/4X/4 PHY IP for 12nm

- Compliant with JEDEC standards for LPDDR5X/5/4X/4 with PHY standards

- DFI 5.0 Interface Compliant

- Supports up to 4 ranks

- Multiple frequency states

-

LPDDR5/4x/4 PHY IP for Samsung 14LPU

- Compliant with JEDEC standards for LPDDR5/4x/4 with PHY standards

- DFI 5.0 Interface Compliant

- Supports 1,2, or 4 ranks

- Multiple frequency states

-

LPDDR4x/4 PHY IP for 22nm

- Compliant for JEDEC standards for LPDDR4x/4 with PHY standards

- DFI Interface Compliant

- Supports 1,2, or 4 ranks

- Multiple frequency states

-

LPDDR5X/5/4X/4 combo PHY at 7nm

- Compliant with JEDEC JESD209-5B for LPDDR5X/5/4X/4 with PHY standards

- Delivering up to 8533Mbps

- DFI 5.1 specification PHY Interface Compliant

- Support up to 4 ranks

-

LPDDR5/4x/4 combo PHY on 14nm, 12nm

- Compliant with JEDEC standards for LPDDR5/4x/4 with PHY standards

- DFI 5.0 Interface Compliant

- Supports 1,2, or 4 ranks

- Multiple frequency states

-

GDDR6 PHY IP for 12nm

- JEDEC JESD250 compliant GDDR6 support

- X16 mode, X8 mode, and pseudo-channel mode

- Low frequency RDQS mode support

-

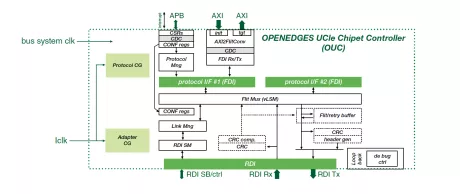

UCIe Die-to-Die Chiplet Controller

- High configurability and customizability

- Defines packets to communicate with a link partner using different AXI parameters

- Supports raw streaming modes

- Provides various Flit formats in UCIe v1.1 (filt format 2: 68B flit format, flit format 3/4: standard 256B flit format, and flit format 5/6: latency optimized 256B flit format)