MIPI D-PHY/ LVDS Combo PHY IP

Filter

Compare

6

IP

from

4

vendors

(1

-

6)

-

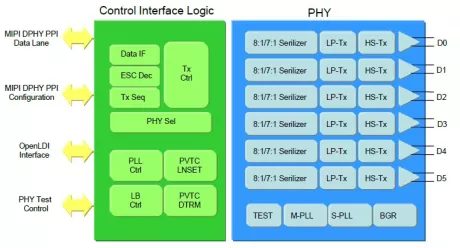

MIPI DPHY & LVDS Transmit Combo on GF55LPe

- MIPI D-PHY version 1.2 compliant PHY transmitter

- OpenLDI version 0.9 compliant LVDS transmitter

-

MIPI D-PHY/LVDS Combo Transmitter IP

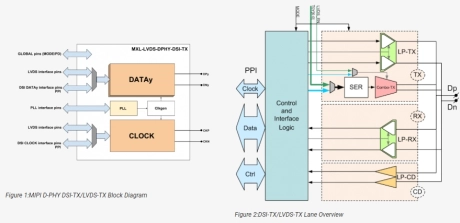

- The MXL-LVDS-DPHY-DSI-TX is a combo PHY that consists of a high-frequency low-power, low-cost, source-synchronous, Physical Layer supporting the MIPI® Alliance Standard for D-PHY and a high performance 4-channel LVDS Serializer implemented using digital CMOS technology.

- In LVDS mode, both the serial and parallel data are organized into 4 channels. The parallel data is 7 bits wide per channel. The input clock is 25MHz to 150MHz. The serializer is highly integrated and requires no external components. The circuit is designed in a modular fashion and desensitized to process variations. This facilitates process migration, and results in a robust design.

-

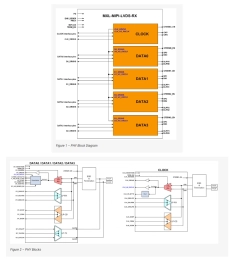

MIPI D-PHY/LVDS Combo Receiver IP

- The MXL-LVDS-MIPI-RX is a high-frequency, low-power, low-cost, source-synchronous, Physical Layer that supports the MIPI® Alliance Standard for D-PHY and compatible with the TIA/EIA-644 LVDS standard.

- The IP is configured as a MIPI slave and consists of 5 lanes: 1 Clock lane and 4 data lanes, which make it suitable for display serial interface applications (DSI).

-

Automotive IP Suite

- Our silicon proven Automotive IP Suite offers versatile and robust IP solutions for high-speed data communication in automotive applications.

- By supporting a wide range of industry standards, it provides automotive manufacturers with the flexibility and reliability needed to develop advanced, high-performance vehicle systems.