MIPI CSI2 Receiver IP

Filter

Compare

43

IP

from

21

vendors

(1

-

10)

-

MIPI CSI-2 V3 RECEIVER INTERFACE IP

- The MIPI CSI-2 (Camera Serial Interface) defines an interface between a peripheral device (camera) and host processor (application engine) for mobile applications

- The MIPI CSI-2 provides the mobile industry a standard, robust, scalable, low-power, high-speed, cost-effective interface that supports a wide range of imaging solutions for mobile devices

-

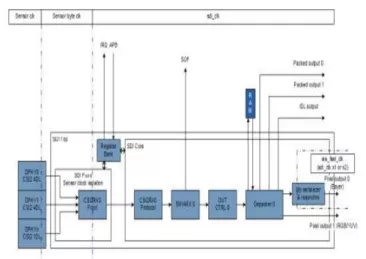

MIPI CSI-2 Receiver IIP

- Compliant with MIPI CSI-2 Specification v1.0, v1.1, v1.3, v2.0,v2.1

- Compliant with D - PHY Specification v1.1,v1.2,v2.0,v2.1

- Compliant with C - PHY Specification v0.7,v1.2,v2.0

- Full MIPI CSI-2 RX functionality where either D - PHY / C - PHY can be used

-

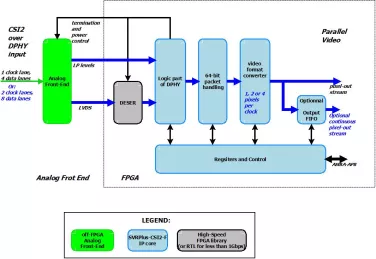

High Performance Second Generation Extended MIPI CSI2 Receiver

- Configurable 1, 2, 3 or 4 data lanes;

- Configurable 1 or 2 clock lanes; 1,2,3,4 or 8 data lanes, when 8 data lanes option is ordered

- 64 bit internal data bus

- Optional 2 and 4 pixels output per clock

-

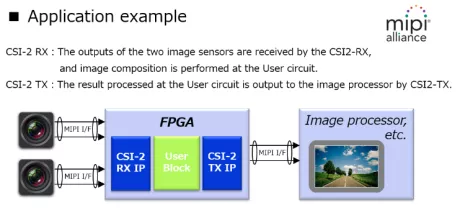

MIPI CSI-2 Receiver for FPGA

- Realize MIPI I/F with Low cost

- Series development for small quantity, large variety

- Available for evaluation of Product development

-

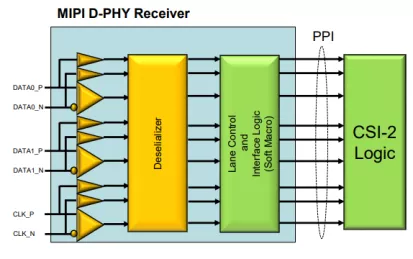

MIPI D-PHY Receiver for CSI-2 of TSMC 40nm LP

- Renesas MIPI D-PHY Receiver can be used for analog Receiver of following interface.

- Technology is TSMC 40nm LP 1p8M (4x2y1z).

- Supply voltage can be applied 1.18V for core voltage, 1.8V for IO voltage.

- Maximum data rate of each channel is 1.0Gbps at High-speed mode.

-

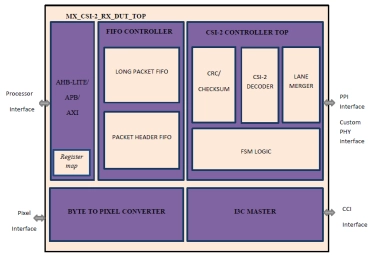

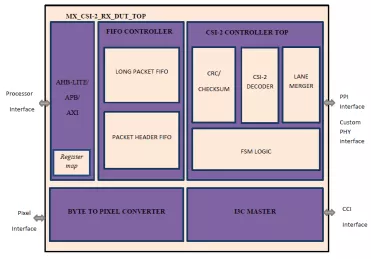

MIPI CSI2 Receiver Interface

- Compliance as per MIPI-CSI-2 version3.0.

- Compliance with C-PHY 2.0 for MIPI CSI-2 Version3.0

- Compliance with D-PHY 2.5 for MIPI CSI-2 Version3.0.

-

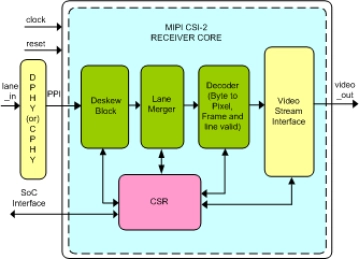

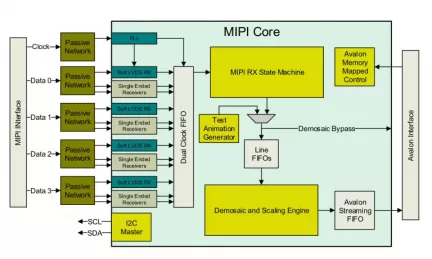

MIPI CSI2 Receiver

- Provides Compatible MIPI D-Phy v1.1 physical layer using FPGA LVDS/LVCMOS IO and passive network

- Supports CSI-2 protocol for unidirectional data transfer

- Compatible with D-PHY Configured for 1 clock and 4 data lanes

- Intended for per-lane clocks rates up to 1 Gbps, depending on device speed grade

-

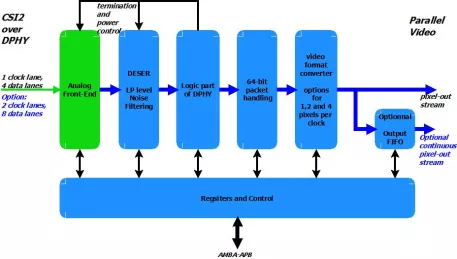

Extended MIPI CSI2 Serial Video Receiver, 64 bits, 8 data lanes, 4 pixels/clock

- 64 bit internal bus

- 8 data lanes, with one or and 2 clock lanes in extended CSI2 mode

- 1,2 or 4 24-bit pixels per clock

- optional BER measurement

-

MIPI CSI-2 Receiver v1.3 Controller IP, Compatible with MIPI C-PHY & D-PHY

- MIPI Alliance Specification for Camera Serial

- Configurable DPHY Interface number

- Configurable Data Lane number (independent for each DPHY I/F)

- Configurable number of each output type