MIPI CSI-2 Transmitter IP

Filter

Compare

38

IP

from

19

vendors

(1

-

10)

-

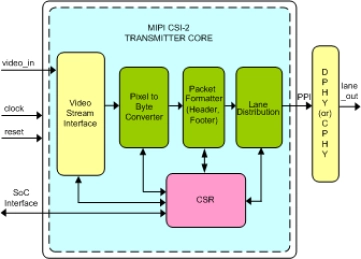

MIPI CSI-2 Transmitter IIP

- Compliant with MIPI CSI-2 Specification v1.0, v1.1, v1.3, v2.0,v2.1

- Compliant with D - PHY Specification v1.1,v1.2,v2.0,v2.1

- Compliant with C - PHY Specification v0.7,v1.2,v2.0

- Full MIPI CSI-2 TRANSMITTER functionality where either D - PHY / C - PHY can be used

-

MIPI CSI -2 TRANSMITTER IP -V3

- MIPI CSI-2 (Camera Serial Interface) Transmitter IP defines an interface between a peripheral device (camera) and host processor (application engine) for mobile applications

- The MIPI CSI-2 Transmitter IP provides the mobile industry a standard, robust, scalable, low-power, high-speed, cost-effective interface that supports a wide range of imaging solutions for mobile devices

-

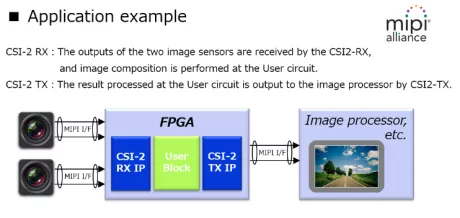

MIPI CSI-2 Transmitter for FPGA

- •Realize MIPI I/F with Low cost

- •Series development for small quantity, large variety

- •Available for evaluation of Product development

- •Data Lane 1~4Lane

-

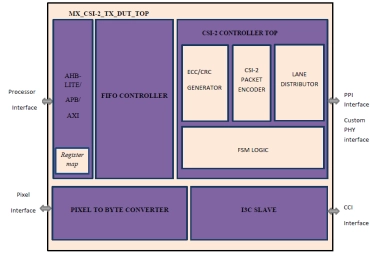

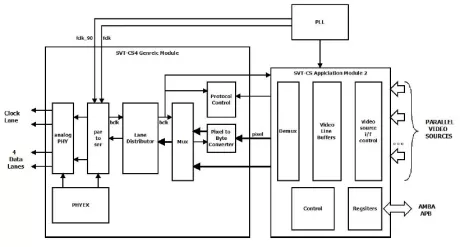

Multi-Video-Source Multiplexing Serial Video Transmitter for MIPI CSI2

- One clock lane, and one to 4 data lanes

- Up to 1.5 Gbps per lane;

- Supports CSI2 RAW8, RAW10, RAW12, all YUV420, all YUV422 and User-Defined 8-bit formats

-

MIPI CSI-2 v3.0 TRANSMITTER FOR COMBO C/DPHY

- Compliant with MIPI CSI Standard v3.x, v2.x, v1.x and MIPI D-PHY Standard v1.x, MIPI D-PHY Standard V2.x and MIPI C- PHY V1.x

- Up to 3 Gsps per trio using C-PHY. 17Gbps in 3 Trios.

- Up to 2.5 Gbps per data lane of D-PHY (V2.0). 10Gbps in 4 Lanes

- Programmable 1, 2, 3 (C-PHY) or 4 (D-PHY) Data Lane Configuration.

-

MIPI CSI2 rev 2.0 transmitter/controller for FPGA, with 8 lanes and 2.5Gbps per lane

- One clock lane, and from 1 to 8 data lanes

- Simple interface – legacy parallel-video input, augmented by an Early-HD signal

-

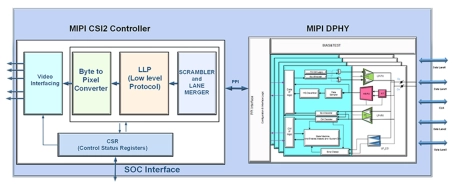

MIPI CSI2 Interface Solution

- Brite provides full solution for the MIPI CSI interface, which receives the data from sensors in PHY layer, and then converts the byte data to pixel after lane data mergence.

- Data scramble is an optional feature to decrease the EMI effect.

- A standard PPI interface is implemented for the connection between MIPI PHY and CSI controller. Brite MIPI CSI interface solution supports image applications with varying pixel formats.

-

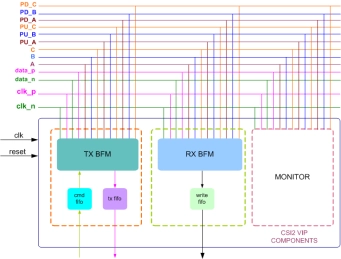

MIPI CSI-2 with C-PHY Verification IP

- Compliant to MIPI CSI-2 Specification Version 4.0.1 along with MIPI C-PHY Specification Version 2.1 with PPI interface

- Supports upto 32 virtual channels with C-PHY

- C-PHY supports MFEN and SFEN for CSI-2 TX and RX respectively for Data Lane greater than 1

- C-PHY supports MFAA and SFAA for CSI-2 TX and RX respectively for Data Lane 1 module

-

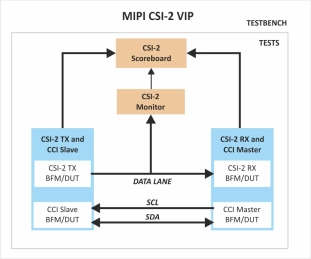

MIPI CSI-2 Verification IP

- Full MIPI CSI2 Tx/Rx functionality

- Compliant with MIPI CSI2 Bus Specification v1.0 to v1.3, v2.0 to v2.10,v3.0,v4.0.

- Supports both DPHY and CPHY.

- Supports forward escape ULPM on all Data Lanes.