M-PCIe IP

Filter

Compare

3

IP

from

1

vendors

(1

-

3)

-

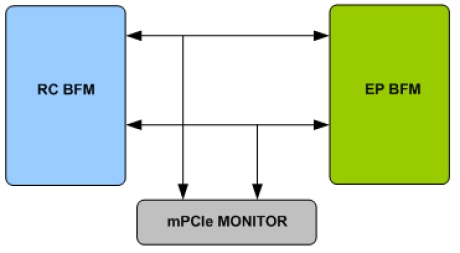

MPCIE Verification IP

- Supports PCIE Express specs 1.0/2.0/3.0/4.0/5.0

- Supports MPHY RMMI and serial interface

- - > All error injections in MPHY layer

- - > All protocol checks for MPHY layer

-

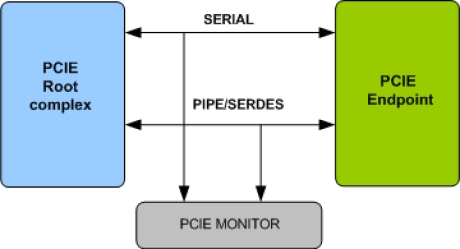

PCI Express Verification IP

- Supports PCI Express specs 1.0/2.0/2.1/3.0/4.0/5.0/6.0

- Supports mPCIe

- Supports PIPE, PCS/PMA, Message Bus and SERDES interface

- Supports MPHY RMMI and serial interface

-

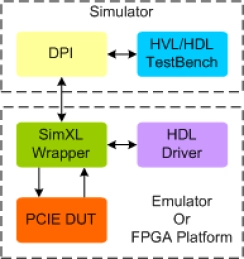

PCI Express Synthesizable Transactor

- Supports PCI Express specs 1.0/2.0/3.0/4.0/5.0/6.0.

- Supports MPCIE

- Supports PIPE, PCS/PMA, and serdes interface

- Supports MPHY RMMI and serial Interface