Low Power Memory Compiler IP

Filter

Compare

196

IP

from

23

vendors

(1

-

10)

-

Low Power Memory Compiler - 1-Port Register File Compiler - GF 22nm FDX

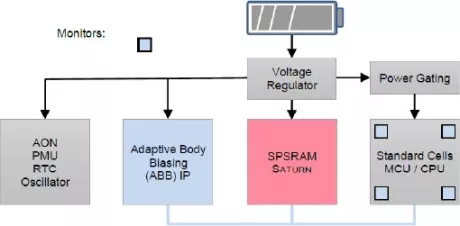

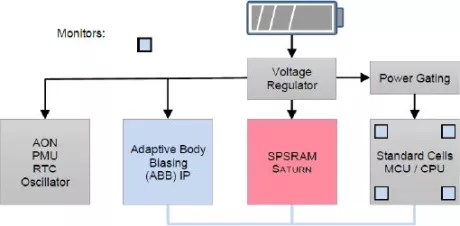

- Specifically designed for ultra-low power applications, this memory leverages body biasing to dramatically reduce power consumption.

- Compatible with industry Adaptive Body Biasing IP for PVT and aging compensation

- Body Biasing functionality (up to +1.3V / -1.5V) to reduce leakage or increase speed at the same power

-

Low Power Memory Compiler - Single Port SRAM - GF 22nm FDX

- Silicon proven Single Port SRAM compiler for GF22 FDX - Memory optimized for low power and supports body biasing.

-

UMC 28nm HPC process standard synchronous high density single port low power SRAM memory compiler with row redundancy

-

UMC 28nm HPC process standard synchronous LVT periphery high density single port low power SRAM memory compiler with row redundancy

-

UMC 28nm HPC process standard synchronous HVT periphery high density single port low power SRAM memory compiler with row redundancy

-

Metal programmable ROM compiler - Memory optimized for low power - compiler range up to 1024 k

- Foundry sponsored memory generator

- For nominal voltage characterization corner

- Configuration

- Dolphin's SVT bit-cell and HVT transistors for periphery

-

Metal programmable ROM compiler - Memory optimized for low power - compiler range up to 256 k

- Foundry sponsored memory generator

- For nominal voltage characterization corner

- Power reduction features

- Up to 50% gain in dynamic power consumption compared to standard ROM

-

Metal programmable ROM compiler - Memory optimized for low power - compiler range up to 1024 k

- Ultra-low-leakage even in a generic process

- No leakage in memory plane

- Minimal leakage in memory periphery while achieving between 230 and 300 MHz in worst case in TSMC 90 nm LP !

- Key patent for high density with only one programming layer

-

Metal programmable ROM compiler - Memory optimized for low power - compiler range up to 256 k

- Power reduction features

- Decrease of packaging cost

- Smaller SoC area

- Decrease of fabrication costs