Interface IP

Filter

Compare

6,635

IP

from

342

vendors

(1

-

10)

-

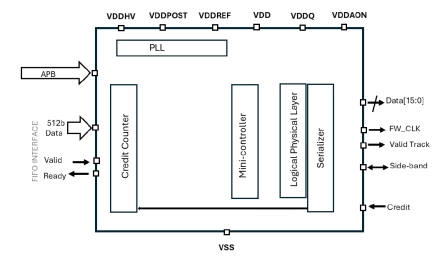

UCIe TX Interface

- Transmit-only UCIe REV1.1 with FIFO Interface

- TSMC 16FFC process

- Low power UCIe D2D

- 1 pJ/bit at 0.7V

-

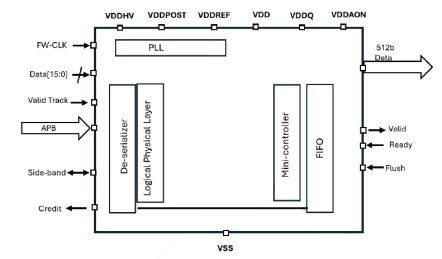

UCIe RX Interface

- Receive-only UCIe Rev1.1 with FIFO Interface

- Samsung 8nm process

- Low power UCIe D2D

- 1 pJ/bit at 0.7V

-

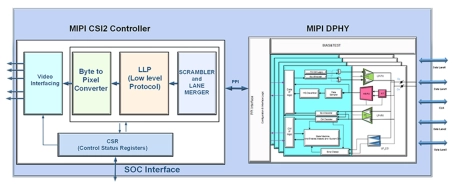

MIPI CSI2 Interface Solution

- Brite provides full solution for the MIPI CSI interface, which receives the data from sensors in PHY layer, and then converts the byte data to pixel after lane data mergence.

- Data scramble is an optional feature to decrease the EMI effect.

- A standard PPI interface is implemented for the connection between MIPI PHY and CSI controller. Brite MIPI CSI interface solution supports image applications with varying pixel formats.

-

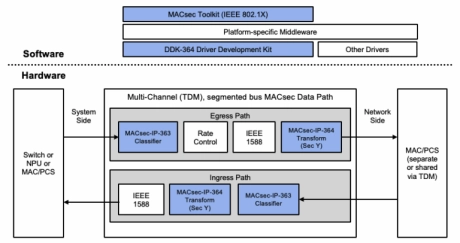

1.6T/3.2T Multi-Channel MACsec Engine with TDM Interface (MACsec-IP-364)

- The MACsec-IP-364 is a MACsec/IPsec engine developed specifically for high-speed, multi-rate and multi-port Ethernet devices.

- Its architecture provides an optimal multi-protocol solution for aggregate throughput for 1.6T and 3.2T.

- The MACsec-IP-364 is ideal for deployment in data center, enterprise and carrier network applications, as well as network-attached high-performance computing.

-

DDR4/LPDDR4 PHY Interface

- The DDR PHY IP is a combination of hard macro, I/O Pad and synthesizable RTL to provide a physical interface to JEDEC standard DDR3/DDR4 SDRAM memories.

- The synthesizable RTL (ddr_phy_top) provides control functions such as initialization, SDRAM interface training, impedance calibration and programmable configuration controls.

-

USB 2.0 HS PHY Interface

- The USB PHY IP is UTMI interface compatible and a dedicated circuit for full-function USB 2.0 transceivers.

- It is a mixed-signal circuit, with the analog part including the transmitting and receiving circuits, level conversion circuits, bus driver circuits, etc., and the digital part including the transmitting and receiving and speed switching control circuits, encoding and decoding circuits, serial-to-parallel and parallel-to-serial conversion circuits, as well as digital CDR circuits, etc.

-

Digital Camera Interface

- Supports image and video capturing of DVP interface camera (GC0308/OV5640)

- Supports image and video capturing of parallel digital video decode chip (TVP5150)

- Supports 8-, 10-, 12-, 14-, 16-bit parallel input data

-

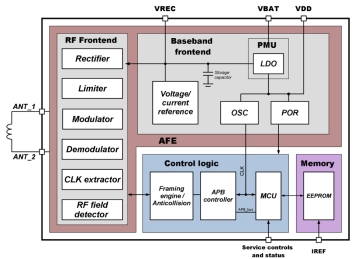

NFC wireless interface supporting ISO14443 A and B with EEPROM on SMIC 180nm

- The IP block provides the physical layer implementation of ISO 14443 interface. In particular, it includes the necessary functional devices for receiving data on the connected antenna, for the response load modulation, received and transmitted data (de)framing and parallel interface to external CPU.

- This IP also can be used for adding NFC functionality to mobile devices and other applications to perform high-level RFID protocol tasks.

-

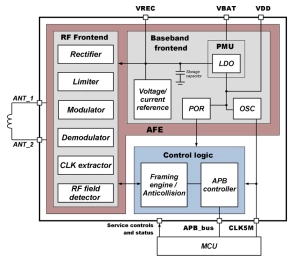

NFC wireless interface supporting ISO14443 A and B on SMIC 180nm

- The IP block provides the physical layer implementation of ISO 14443 interface. In particular, it includes the necessary functional devices for receiving data on the connected antenna, for the response load modulation, received and transmitted data (de)framing and parallel interface to external CPU.

- This IP also can be used for adding NFC functionality to mobile devices and other applications to perform high-level RFID protocol tasks.

-

ION 64b66b IP (64b/66b High-speed Serial Interface)

- ION 64b66b is an IP for high-speed serial interface targeting applications with inter-chip and inter-board connections.

- Lightweight link layer protocol provides one-to-one data movement via one or more high-speed serial lanes.