Half-Power SERDES IP

Filter

Compare

10

IP

from

4

vendors

(1

-

10)

-

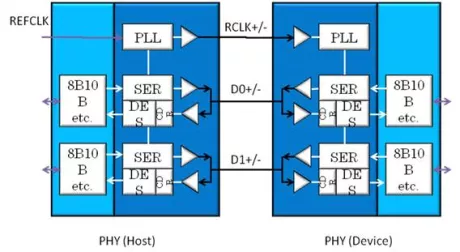

UHS2 Host Phy

- SD Specifications Part 1 UHS-II Specification Volume 2: PHY Draft Version 0.9

- SD Specifications Part 1 UHS-II Specification Volume 1: System and Protocol Draft Version 0.91

- (Will be SD4.0 Version1.0 compliance when the standard is released)

- Bi-directional receiver/transmitter (2ch) supporting both Full Duplex and Half Duplex modes

-

UHS2 Device Phy

- SD Specifications Part 1 UHS-II Specification Volume 2: PHY Draft Version 0.9

- SD Specifications Part 1 UHS-II Specification Volume 1: System and Protocol Draft Version 0.91

- (Will be SD4.0 Version1.0 compliance when the standard is released)

- Bi-directional receiver/transmitter (2ch) supporting both Full Duplex and Half Duplex modes

-

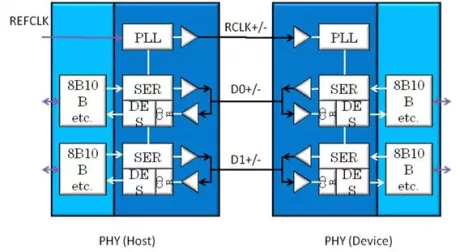

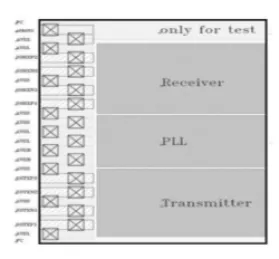

SD4.x UHSII

- Fully compliant with UHSII specification Ver. 4.x

- Bidirectional receiver/transmitter (2 channels) supporting both full and half duplex modes

- Supports data rates from 390Mbps to 1.56Gbps/ch

- RCLK frequency: 26 to 56MHz

- Built-in PLL and clock recovery

-

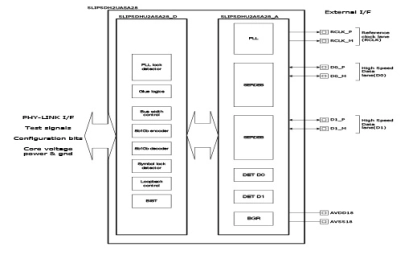

Simulation VIP for PCIe

- Device Type

- Root Complex, End Point, Legacy End Point, Switch, PHY DUT, Bridge

- Interface

- Serial, Parallel (8-bit, 10-bit, 128-bit, and 130-bit), PIE8, PIPE 3.0, PIPE 4.0, PIPE 4.3, PIPE 4.4.x, PIPE 5.x, PIPE 6.0

-

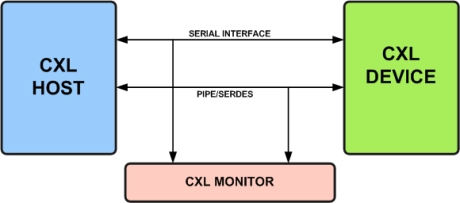

CXL Verification IP

- Supports CXL specs revision 1.0, 1,1 and 2.0.

- Supports Native PCIe mode and below features as defined in the PCIe specification.

- PCIE Express specs 1.0/2.0/3.0/4.0/5.0/5.1

- Serial, PIPE, PCS/PMA, Low pin count and SerDes interface

-

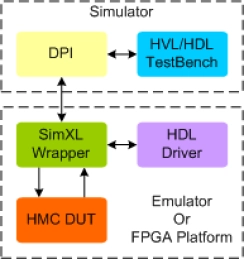

HMC Synthesizable Transactor

- Supports 100% of HMC protocol standard 1.0, 2.0 and 2.1

- Supports all the HMC commands as per the specs

- Supports 2,4 and 8 link configuration

- Supports for half width(8-lanes) and full width(16-lanes)

-

USB 3.1 Type-C PHY IP, Silicon Proven in TSMC 55ULP

- Support half rate mode (5Gbps) and full rate mode (10Gbps)

- Tolerate max +/-7000ppm input frequency offset

- 32bit/40bit selectable parallel data bus

- Programmable transmit amplitude

-

USB 3.1 Type-C PHY IP, Silicon Proven in SMIC 12SF++

- Support half rate mode (5Gbps) and full rate mode (10Gbps)

- Tolerate max +/-7000ppm input frequency offset

- 32bit/40bit selectable parallel data bus

- Programmable transmit amplitude

-

USB-C 3.1 SS/SSP PHY, Type-C IP (Silicon proven in UMC 55SP/ EF)

- Support half rate mode (5Gbps) and full rate mode (10Gbps)

- Tolerate max +/-7000ppm input frequency offset

- 32bit/40bit selectable parallel data bus

- Programmable transmit amplitude

-

SD4.1 UHS- II PHY IP

- SD 4.1 compliant SDHC/SDXC UHS-II Physical Layer for Host

- 16bit interface to Link layer

- Supports both Full Duplex mode and Half Duplex mode