HBM4 IP

Filter

Compare

8

IP

from

6

vendors

(1

-

8)

-

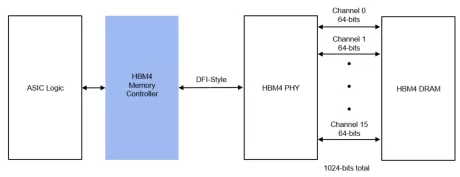

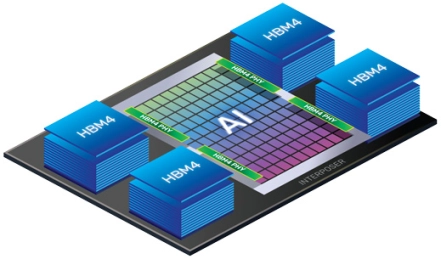

HBM4 PHY IP

- Supports JEDEC HBM4 DRAMs

- Supports data rates up to 12 Gbps

- Supports up to 32 independent 64-bit memory channels

- Pseudo-channel operation supported to enable up to 64 32-bit pseudo-channels with 2048-bit PHY

-

HBM4 Controller IP

- Supports JEDEC standard HB4 DRAM

- DFI 5.1 compliant interface to HBM4 PHY

- Multiport Arm® AMBA® interface (AXI™) with managed QoS per pseudo-channel or single-port host interface(HIF), per channel

-

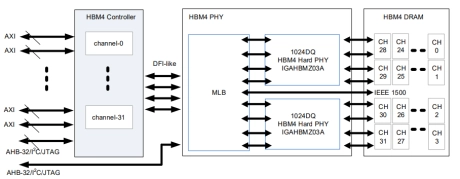

TSMC CLN3FFP HBM4 PHY

- IGAHBMZ03A is a High Bandwidth Memory 4 Physical Layer (HBM4 PHY) that is compliant with JEDEC HBM4 DRAM Specification JESD270-4.

- Fabricated in the TSMC 3 nm Advanced process node (N3P), it supports the data rate up to 12 Gbps per data pin in the DDR PHY Interface (DFI)-like 1:4 clock frequency ratio (HBM4 controller clock: WDQS = 1:4).

-

HBM4 Memory Controller

- Supports HBM4 memory devices

- Supports all standard HBM4 channel densities (up to 32 Gb)

- Supports up to 10 Gbps/pin

- Refresh Management (RFM) support

- Maximize memory bandwidth and minimizes latency via Look Ahead command processing

- Integrated Reorder functionality

-

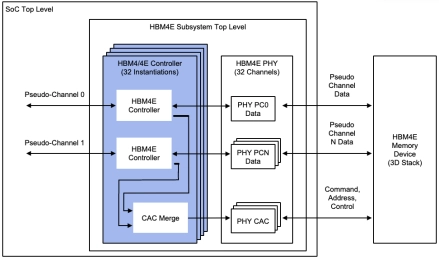

HBM4E Controller IP

- Supports HBM4/4E memory devices

- Supports all standard HBM4 channel densities (up to 32 Gb)

- Supports up to 16 Gbps/pin

- Refresh Management (RFM) support

-

HBM4E PHY and controller

- Advanced clocking architecture minimizes clock jitter

- DFI PHY Independent Mode for initialization and training

- IEEE 1500 interface, memory BIST feature, and loop-back function

- Supports lane repair

-

HBM4/3E Combo PHY & Controller

- The fourth-generation and third-generation HBM (HBM4/3E) technology is outlined by the JESD238A standard (for HBM3E) and an upcoming specification (for HBM4)

- These technologies feature 256-bit memory access per channel, with a 1024-bit input/output interface for HBM3E and up to a 2048-bit interface for HBM4

-

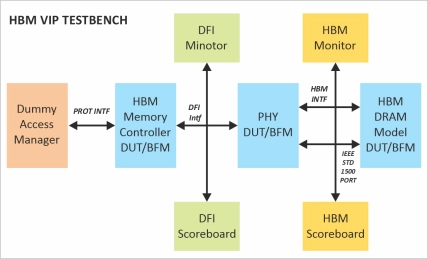

HBM 4 Verification IP

- The HBM4 Verification IP provides an effective & efficient way to verify the components interfacing with HBM interface of an ASIC/FPGA or SoC.

- The HBM4 VIP is fully compliant with Standard HBM Version JESD270-4 specifications from JEDEC.

- This VIP is a light weight VIP with easy plug-and-play interface so that there is no hit on the design time and the simulation time.