Flex Logix IP

Filter

Compare

5

IP

from

5

vendors

(1

-

5)

-

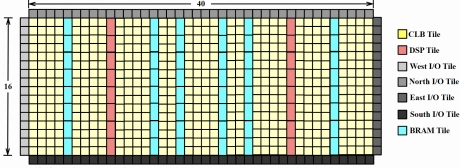

eFPGA IP — Flexible Reconfigurable Logic Acceleration Core

- RapidFlex eFPGA IP provides a reconfigurable, upgradeable, and iterative logic computing layer for SoCs, MCUs, AI accelerators, industrial control, and communication chips.

- Based on RapidFlex's self-developed ArkAngel® toolchain (AAEE), our eFPGA core delivers full-flow capabilities from architecture exploration → RTL → physical implementation (GDSII) → digital design flow verification, leading the industry in performance density, integrability, and toolchain experience.

-

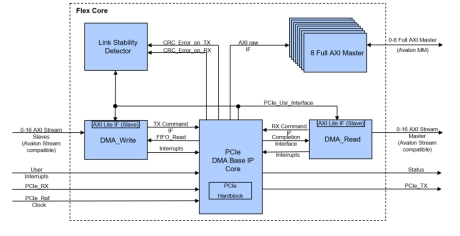

Multi-Channel Flex DMA IP Core for PCI Express

- The Multi-Channel DMA IP Core for PCI-Express is a powerful PCIe Endpoint with multiple industry standard AXI Interfaces.

- Up to 16 independent AXI Stream Slaves write DMA Data to the Host. Up to 16 AXI Stream Masters read DMA Data from the Host and present it to the User Logic.

- Each channel operates on a separate memory area. Additional 8 AXI4 Masters are available to interface full AXI or AXI-Lite peripherals with the Host.

-

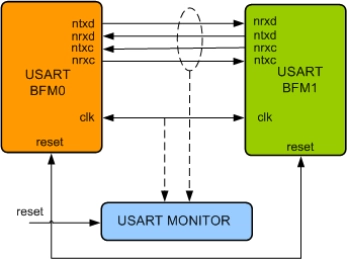

USART Verification IP

- Fully compatible with ds8251.

- Transmit and receive commands allow the user to transmit and receive USART data.

- Configurable Baud rate.

- Programmable word length, stop bits, and parity

-

Intel® Stratix® 10 FPGA H-Tile Hard IP for Ethernet Intel® FPGA IP Core

- Intel® Stratix® 10 FPGA H-Tile FPGA production devices include a configurable, hardened protocol stack for Ethernet that is compatible with the IEEE 802.3 High Speed Ethernet Standard.

-

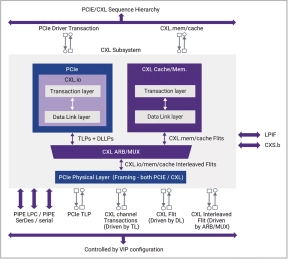

VIP for Compute Express Link (CXL)

- Native SystemVerilog/UVM

- Source Code Test Suites Available

- Built-in Protocol Checks

- Complete Subsystem Verification Solution