Encryption IP

Filter

Compare

502

IP

from

73

vendors

(1

-

10)

-

AES-SX-ULP-full Secure Core - High-Performance, Ultra Low-Power AES Encryption Core with Full Mode Support and Formally Proven SCA Protection

- High-Performance, Ultra Low-Power AES Encryption Core with Full Mode Support and Formally Proven SCA Protection

-

AES-SX-ULP-full Secure Core - High-Performance/Ultra Low Power AES Encryption Core with Full Mode Support and Formally Proven SCA Protection

-

AES-SX-ULP-full Secure Core - Ultra-Low-Power AES Encryption Core with Full Mode Support and Formally Proven SCA Protection

- Ultra-Low-Power AES Encryption Core with Full Mode Support and Formally Proven SCA Protection

-

AES-SX-GCM-XTS-up Secure Core - AES Encryption Core with Extreme SCA Protection for Ultra-High-Security Applications

- The Ultra-Secure AES IP core is designed for applications where maximum resistance to side-channel attacks (SCA) is paramount, even beyond certification-grade requirements.

- Supporting AES-128/256 encryption in ECB, CBC, CTR, GCM, and XTS modes, the core is built for environments where redundancy in protection is a feature, not a cost.

-

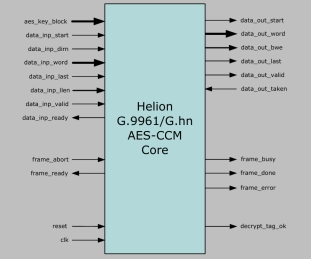

G.9961 AES-CCM Frame Encryption Core

- The Helion G.9961 AES-CCM (“AES-G.hn”) core is designed to sit near the top of the LLC sublayer and provide the security functionality described in Section 9.1 of ITU-T G.9961.

- The core integrates all of the underlying functions required to implement AES in CCM mode for G.9961 including nonce and header formation, round-key expansion, counter management, block chaining, final block masking, and tag appending and checking features.

- The only external logic required is to insert the CCMP header field for frames that are to be encrypted.

-

Stealth AES Encryption IP

- The Stealth AES Encryption IP provides advanced encryption capabilities to secure data transmission and storage in various applications, including IoT devices, edge computing systems, cloud platforms, and communication networks.

- Built on the Advanced Encryption Standard (AES), our IP offers robust encryption algorithms to safeguard sensitive information against unauthorized access and data breaches.

-

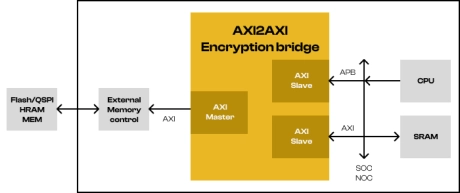

AXI2AXI encryption bridge

- The PLUG module is a silicon-proven AXI-to-AXI bridge designed to provide data encryption and inline ECC for reliable and secure communication.

- It supports AXI4 protocol with bursts and integrates seamlessly into systems handling DMA, CPU, or cache streams.

- For write transactions, it encrypts data and appends ECC, while for reads, it decrypts and validates/corrects ECC.

-

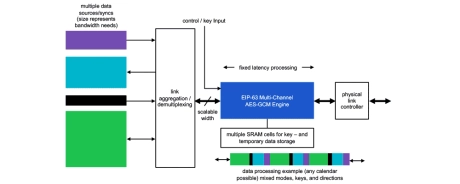

Inline cipher engine for PCIe, CXL, NVMe, 5G FlexE link integrity and data encryption (IDE) using AES GCM mode

- The ICE-IP-63 (EIP-63) is a scalable high-performance, multi-channel cryptographic engine that offers AES-GCM operations as well as AES-CTR and GMAC on bulk data.

- Its flexible data path is suitable to scale from 100 Gbps to 2.4 Tbps to provide a tailored engine with minimal area for your application.

- The FIFO-like data interface makes it possible to perform frame processing for many different protocols, including MACsec, IPsec, and OTN security.

-

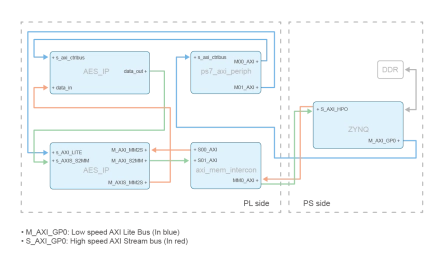

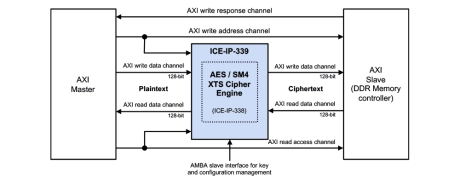

Inline cipher engine with AXI, for memory encryption

- Throughput: 128 bit (16 Byte) wide encryption/decryption per cycle

- Throughput: 1 tweak computation per 4 clock cycles

- Bidirectional design including arbitration between read and write requests

- Zero clock overhead for switching between encryption (write) and decryption (read)

- 30-40 cycle data channel latency

-

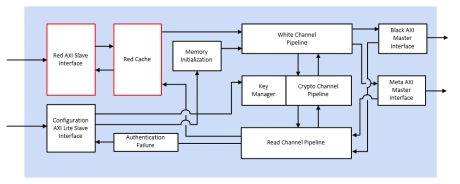

Inline memory encryption engine, for FPGA

- Performs encryption, decryption and/or authentication using AES Counter Mode (CTR) or Galois Counter Mode (GCM)

- Supports AES key sizes 128 or 256

- Internal key management with NIST-compliant key generation

- Encrypt memory space into user-defined vaults, each with a unique key

- Compatible with AMBA AXI4 interface

- Supports hard or soft memory controllers in Xilinx FPGA and SoC devices

- Supports multiprocessor systems