ETIS ORI 4.1.1 CPRI IQ Compression IP

Filter

Compare

106

IP

from

24

vendors

(1

-

10)

-

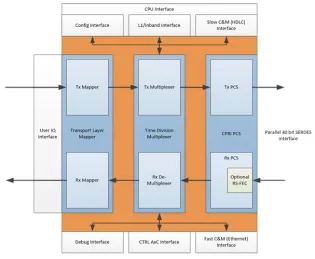

Common Public Radio Interface (CPRI) v.7.0 IPC

- Conforming to CPRI v.7.0: 2015-10-09 Specification

- Support for REC / RE applications

-

Common Public Radio Interface (CPRI) v.6.1 IPC

- Standards: CPRI v.6.1: 2014-07-01 [CPRI] and earlier

- Air Interfaces Supported: 3GPP GSM/EDGE RAN R9, 3GPP UTRA (UMTS WCDMA), 3GP-E-UTRA (LTE), IEEEE 802.16 (WiMAX)

-

Common Public Radio Interface (CPRI) v.5.0 IPC

- Standards: CPRI v.5.0: 2011-09-29 [CPRI] and earlier

- Air Interfaces Supported: 3GPP GSM/EDGE RAN R9, 3GPP UTRA (UMTS WCDMA), 3GP-E-UTRA (LTE), IEEEE 802.16 (WiMAX)

- Applications and Technologies Supported: REC

- Line Baud Rates: From 614.4 Mbps up to 9.830 Gbps

-

Common Public Radio Interface (CPRI) v.4.2 IPC

- Standards: CPRI v.4.2: 2010-09-29 [CPRI] and earlier

- Air Interfaces Supported: 3GPP UTRA (UMTS WCDMA), 3GP-E-UTRA (LTE) IEEEE 802.16 (WiMAX)

- Applications and Technologies Supported: REC

- Line Baud Rates: From 614.4 Mbps up to 9.830 Gbps

-

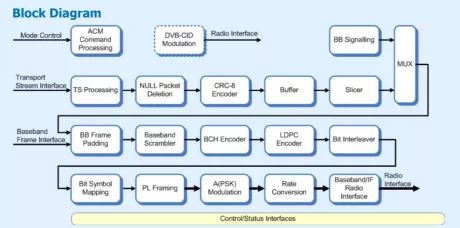

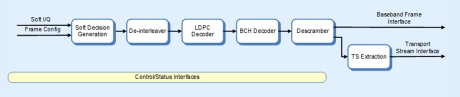

DVB-Satellite FEC Decoder

- The CMS0077 Satellite FEC Decoder has been designed specifically to meet the requirements of the DVB-S2 and DVB-S2X advanced wide-band digital satellite standards.

- The core provides all the necessary processing steps to convert a demodulated complex I/Q signal into a standard TS output stream.

-

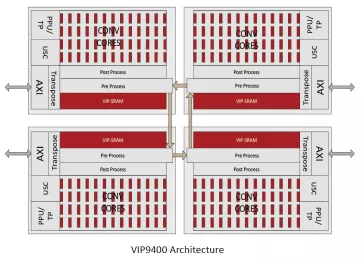

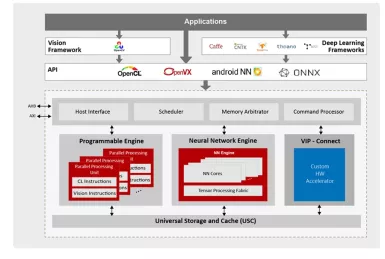

NPU IP for Data Center and Automotive

- 128-bit vector processing unit (shader + ext)

- OpenCL 1.2 shader instruction set

- Enhanced vision instruction set (EVIS)

- INT 8/16/32b, Float 16/32b in PPU

- Convolution layers

-

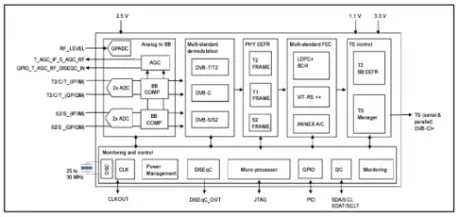

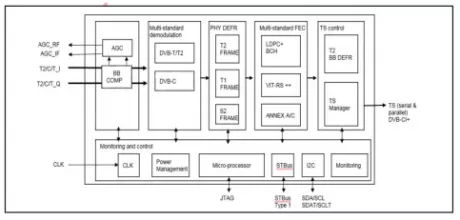

DVB-S2/S/T2/T/C Combo Demodulator IP (Silicon Proven)

- Combines a configurable DVB-T2/T/C/S/S2 demodulator.

- AGC derived from IF

- Low-power process, design and architecture

- Includes full suite of low-level drivers and application software, detailed user manuals and reference design schematics

-

DVB-C Demodulator IP (Silicon Proven)

- QAM and FEC solution

- ITU-T J.83 Annexes A/B/C, DVB-C specification (ETSI 300 429)

- Nordig Unified v2.4 and SARFT compliant

- Up to 7.2 Ms/s symbol rate

-

NPU IP for AI Vision and AI Voice

- 128-bit vector processing unit (shader + ext)

- OpenCL 3.0 shader instruction set

- Enhanced vision instruction set (EVIS)

- INT 8/16/32b, Float 16/32b

-

DVB-S2/S Demodulator and Decoder IP (Silicon Proven)

- Compatible with all ACM (Adaptive Coding and Modulation), VCM (Variable Coding and Modulation) and CCM (Constant Coding and Modulation) configurations of ETSI EN 302 307-1 and ETSI EN 302 307-2.

- Frame-by-frame selection of frame size, FEC code rate and modulation format (QPSK, 8PSK, 16APSK and 32APSK).

- Support for DVB-S2 extensions (S2X) FEC code-rates and modulation formats (64APSK, 128APSK and 256APSK)

- Support for an arbitrary range of symbol rates up to 40% of the master clock frequency