Cadence PCI Express IP

Filter

Compare

18

IP

from

1

vendors

(1

-

10)

-

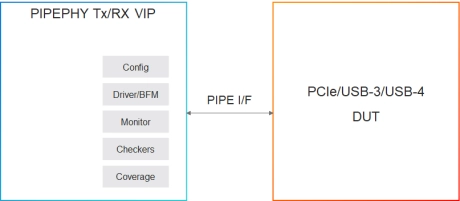

Simulation VIP for PIPE PHY

- Device Type

- PipeXceiver

- SerialXceiver

- PHYDUT Monitor

-

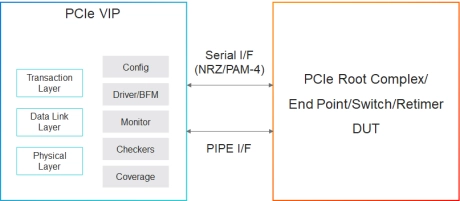

Simulation VIP for PCIe

- Device Type

- Root Complex, End Point, Legacy End Point, Switch, PHY DUT, Bridge

- Interface

- Serial, Parallel (8-bit, 10-bit, 128-bit, and 130-bit), PIE8, PIPE 3.0, PIPE 4.0, PIPE 4.3, PIPE 4.4.x, PIPE 5.x, PIPE 6.0

-

Simulation VIP for NVMe

- Admin Command Set

- Supports all of the mandatory Admin Command set, which defines the commands that can be submitted to the Admin Submission Queue

- NVM Command Set

- Supports all of the mandatory NVM command set, which is a specification-defined I/O command set used with an I/O queue pair

-

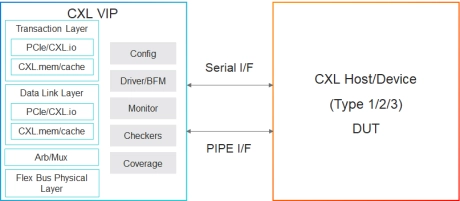

Simulation VIP for CXL

- Device Configuration

- Host, Device

- Spec Version

- 1.1, 2.0, 3.0

-

PHY for PCIe 6.0 and CXL for TSMC 5nm FinFet

- DSP-based Long Reach (LR) equalization and clock data recovery (CDR) provide superior performance and reliability

- Low active and standby power consumption, supports L1 sub-states standby power management

- Extensive set of isolation, test modes, and loopbacks including APB and JTAG

- Supports lane aggregation and bifurcation

-

PHY for PCIe 5.0 and CXL for TSMC 7nm FinFet

- High-performance PHY for data center applications

- Low-latency, long-reach, and low-power modes

- Wide range of protocols that support networking, storage, and computing applications

- Multi-protocol support for application flexibility

-

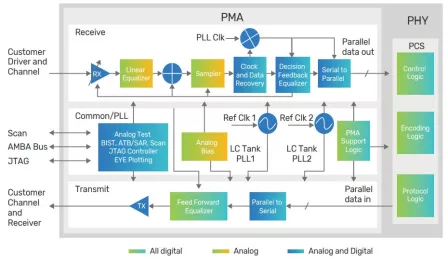

10Gbps Multi-Protocol PHY IP (+PCIe 3.1)

- Supports 10G-KR, PCIe 3.1/2.0/1.0, XAUI, Q/SGMII, and Gigabit Ethernet

- LC tank PLL with a wide range of reference clock frequencies and SSC

- High-performance decision feedback equalization and adaptive CTLE

- Serial and parallel loop-back functions

- Available in X1 through X10 lane configurations

-

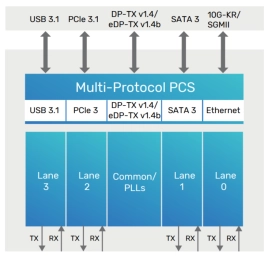

10Gbps Multi-Link and Multi-Protocol PCIe 3.1 PHY IP for TSMC

- Supports USB 3.1, PCIe 3.0/2.0/1.0, DP-TX v1.4/ eDP-TX v1.4b, SATA 3, 10G-KR and SGMII

- Supports PCIe L1 sub-states

- Supports SRIS and internal SSC generation

- Supports internal and external clock sources with clock active detection

-

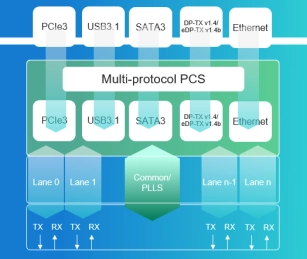

USB 3.1 PHY

- Supports USB 3.1, PCIe 3.1, DP-TX v1.4/eDP-TX v1.4b, SATA 3, 10G-KR and QSGMII/SGMII

- Multi-protocol support for simultaneous independent links

- Supports SRIS and internal SSC generation

- Supports PCIe L1 sub-states

- Automatic calibration of on-chip termination resistors

-

PHY for PCIe 7.0 and CXL

- Architecture optimized for HPC, AI/ML, storage, and networking

- Ultra-long reach, low latency, and low power

- Advanced DSP delivers unmatched performance and reliability

- Comprehensive real-time diagnostic, monitor, and test features

- Bifurcation support for x1, x2, x4, x8, and x16 lanes