10Gbps Multi-Link and Multi-Protocol PCIe 3.1 PHY IP for TSMC

SerDes requirements for system-on-chip (SoC) designs are becoming increasingly demanding and must support increasing numbers of p…

Overview

SerDes requirements for system-on-chip (SoC) designs are becoming increasingly demanding and must support increasing numbers of protocols that must be optimized for cost-and power-sensitive mobile, wireless IoT, consumer, and automotive designs.

The Cadence 10Gbps multi-protocol PHY IP provides a flexible PHY IP that simplifies the design process without compromising performance, power, or silicon die area (PPA). The PHY IP is a lower-active and low-leakage power design crafted for mobile, wireless IoT, consumer, and automotive designs.

The PHY IP is designed for multi-protocols running on single PHY macro and is compliant with USB 3.1, PCI Express (PCIe) 3.1, DisplayPort TX v1.4, Embedded DisplayPort TX v1.4b, SATA 3, QSGMII, and SGMII specifications. The PCS complies with the PIPE 4.2 interfaces, and provides support for the dynamic equalization features of different protocols.

The PHY IP is architected to quickly and easily integrate into any SoC, and to connect seamlessly to Cadence or third-party PIPE-compliant controllers. It provides a cost-effective, versatile, and low-power solution for demanding applications. It offers SoC integrators the advanced capabilities, flexibility, and support that meet the requirements of high-performance designs.

The PHY IP is part of the comprehensive Cadence Design IP portfolio comprised of interface, memory, analog, and system and peripheral IP.

Product Details

The PHY IP is a hard PHY macro available for TSMC processes. I/O pads and ESD structures are included. It is designed to easily integrate with a Cadence Controller IP for PCIe and USB, or any third-party controller with a PIPE-compliant interface. Raw SerDes interface is adopted for Ethernet and DisplayPort protocols.

PHY Architecture

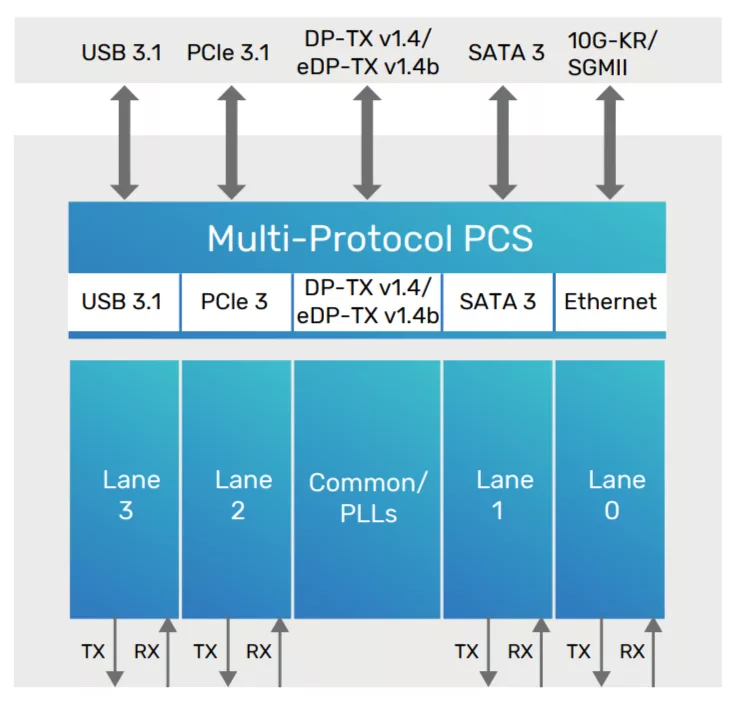

The PHY IP macro consists of a Physical Media Attachment (PMA) layer and a Physical Coding Sublayer (PCS). The Multi-Protocol and Multi-Link architecture PHY IP is highly configurable, allowing the PHY to be easily configured to your specific needs.

The PHY IP is designed with a lane-based architecture featuring one common support for up to eight lanes, providing greater control over floorplanning, placement, packaging, and I/O integration than other hard PHY solutions, while maintaining the reliability and ease of use associated with GDSII macros.

The PCS portion of the PHY provides the control, encoding, and protocol logic. The architecture partitions the PMA core into different primary sub-modules: common PLL, transmitter, and receiver lane modules. The PMA block provides the transmit, common PLL, and receive functions. The common PLL module also provides the interface between SCAN, Arm AMBA Bus, and JTAG and Analog Test including BIST, ABT, Scan, JTAG control, eye plotting, and PMA support logic functions.

The transmitter module converts parallel data from the PCS interface to a serial data stream. The receiver module converts an input serial data stream to parallel data going to the PCS interface.

Key features

- Supports USB 3.1, PCIe 3.0/2.0/1.0, DP-TX v1.4/ eDP-TX v1.4b, SATA 3, 10G-KR and SGMII

- Supports PCIe L1 sub-states

- Supports SRIS and internal SSC generation

- Supports internal and external clock sources with clock active detection

- Multi-protocol support for simultaneous independent links

- Automatic calibration of on-chip termination resistors

- Flexible lane configuration from 1 to 8 lanes

- SCAN, BIST, and serial/parallel loopback functions

Block Diagram

Applications

- Communications,

- Consumer Electronics,

- Data Processing,

- Industrial and Medical,

- Military/Civil Aerospace

What’s Included?

- Standard integration views: LEF abstract, timing views (.LIB), behavioral model (Verily), gate-level netlist, SDF, DRC, LVS, ANT reports, and GDSII layout and layer map

- Synthesizable soft PCS with SDC

- f Complete documentation including user guide, integration guide, and programmer guide

- High Volume Manufacturing (HVM) kit

- Testboards available upon request

Files

Note: some files may require an NDA depending on provider policy.

Silicon Options

| Foundry | Node | Process | Maturity |

|---|---|---|---|

| TSMC | 7nm | N7+ | Silicon Proven |

Specifications

Identity

Provider

Learn more about Multi-Protocol PHY IP core

How a 16Gbps Multi-link, Multi-protocol SerDes PHY Can Transform Datacenter Connectivity

16Gbps SerDes Multiprotocol Multilink PHY IP

32G Multi-Protocol SerDes PHY Out the Gate

New 16Gbps Multi-link, Multi-protocol SerDes PHY Enhances Datacenter Connectivity

One PHY, Zero Tradeoffs: Multi-Protocol PHY for Edge AI Interface Consolidation

Frequently asked questions about Multi-Protocol PHY IP cores

What is 10Gbps Multi-Link and Multi-Protocol PCIe 3.1 PHY IP for TSMC?

10Gbps Multi-Link and Multi-Protocol PCIe 3.1 PHY IP for TSMC is a Multi-Protocol PHY IP core from Cadence Design Systems, Inc. listed on Semi IP Hub. It is listed with support for tsmc Silicon Proven.

How should engineers evaluate this Multi-Protocol PHY?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Multi-Protocol PHY IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.