USB 3.1 PHY

Proven PHY IP for USB3.1 with supporting multi-protocol feature The ® IP for 10Gbps Multi-Protocol PHY simplifies the design proc…

Overview

Proven PHY IP for USB3.1 with supporting multi-protocol feature

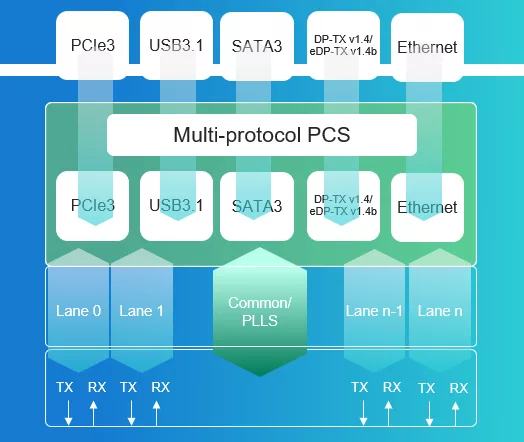

The ® IP for 10Gbps Multi-Protocol PHY simplifies the design process without compromising performance, power, or silicon die area. Crafted for mobile, wireless IoT, consumer, and automotive designs, the IP is designed for multi-protocols running on a single PHY macro and is compliant with USB 3.1, PCI Express® (PCIe®) 3.1, DisplayPort TX v1.4, Embedded DisplayPort TX v1.4b, SATA 3, 10G-KR and QSGMII/SGMII.

Key features

- Supports USB 3.1, PCIe 3.1, DP-TX v1.4/eDP-TX v1.4b, SATA 3, 10G-KR and QSGMII/SGMII

- Multi-protocol support for simultaneous independent links

- Supports SRIS and internal SSC generation

- Supports PCIe L1 sub-states

- Automatic calibration of on-chip termination resistors

- Supports internal and external clock sources with clock active detection

- SCAN, BIST, and serial/parallel loopback functions

Block Diagram

Specifications

Identity

Provider

Learn more about Single-Protocol PHY IP core

Design IP Faster: Introducing the C~ High-Level Language

Universal Flash Storage: Mobilize Your Data

Can MIPI and MDDI Co-Exist?

Enter the Inner Sanctum of RapidIO: Part 1

Networking software key to PICMG 2.16 optimization

Frequently asked questions about Single-Protocol PHY IP

What is USB 3.1 PHY?

USB 3.1 PHY is a Single-Protocol PHY IP core from Cadence Design Systems, Inc. listed on Semi IP Hub.

How should engineers evaluate this Single-Protocol PHY?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Single-Protocol PHY IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.