Arrow Devices IP

Filter

Compare

15

IP

from

13

vendors

(1

-

10)

-

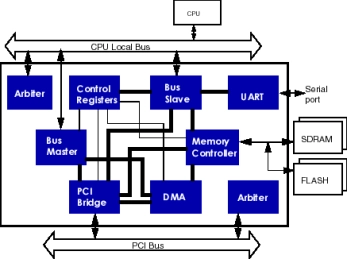

System Controller

- The system controller core connects the system CPU to system memory, PCI bus, IO ports and external communication links.

- While the CPU’s task in the system is to process data, the system controller’s main function is to coordinate data movement in the system.

- The system controller contains all the major functional modules required for most System-on-Chip (SOC) application.

-

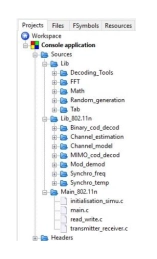

802.11ax PHY Layer C Floating-Point Code IP for the STA mode

- This IP includes a recommendation-compliant 802.11ax PHY layer C floating-point code for the Station (STA) mode.

- The code is integrated into a simulation environment that allows the configuration of mandatory features and the performance evaluation in terms of frame error rate.

- It is designed to generate fixed-point sequences in order to accelerate the development of both C fixed-point code and HDL code for prototyping environments.

-

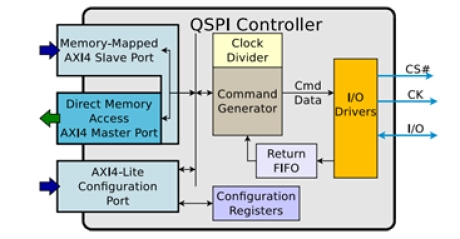

QSPI Master IP

- The QSPI master core is easy to use, simple to work with, quick to operate, and reliable under all conditions.

- It supports the majority of QSPI devices standard from a standard AXI4 slave interface. It also features support for Octal SPI, Dual SPI (DSPI), and SPI interface.

-

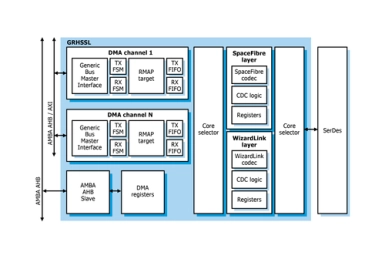

SpaceFibre and WizardLink Interface

- SpaceFibre codec designed according to the SpaceFibre specification ECSS-E-ST-50-11C, single-lane implementation

- WizardLink codec designed to interface with Texas Instrument TLK2711 transceiver

- The IP can inter-operate with off-chip SerDes devices or with FPGA/ASIC hard macros

- Optional 8b10b encoding

-

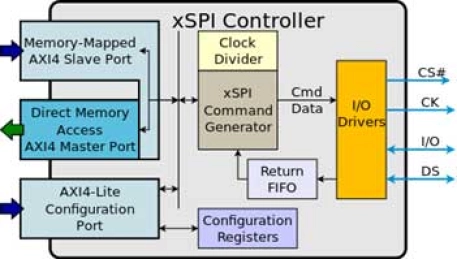

xSPI Master IP | NOR IP

This Universal NOR Flash IP supports a variety of NOR Devices and multiple Protocols, combines ease of use with high reliability, low power and speed under all conditions, including automotive applications.

The xSPI master IP supports the xSPI JESD251 standard from a standard AXI4 slave interface, and also features backwards compatibility support for Octal SPI, QSPI, DSPI, and SPI interfaces. Also supports JEDEC SFDP Standard.

-

QDR II SRAM Controller Intel® FPGA IP Function

- The QDR II SRAM Controller Intel FPGA IP provides an easy-to-use interface to QDR II SRAM and QDR II+ SRAM modules

- The QDR II SRAM controller ensures that the placement and timing are in line with QDR II specifications

- The QDR II SRAM controller’s local interface is compatible with the Intel FPGA Avalon® Memory-Mapped interface, for easy integration into Intel Qsys IP.

-

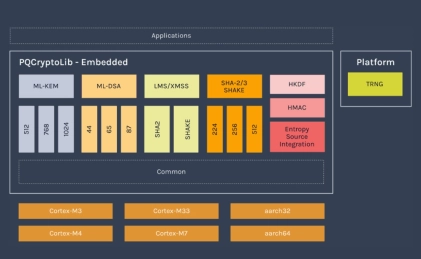

Highly-optimized PQC implementations, capable of running PQC in under 15kb RAM

- PQCryptoLib-Emebedded is a versatile, CAVP-ready cryptography library designed and optimized for embedded devices.

- With its design focused on ultra-small memory footprint, PQCryptoLib-Embedded solutions have been specically designed for embedded systems, microcontrollers and memory-constrained devices. It provides a PQC integration to devices already in the field.

-

SAS INITIATOR IIP

- Supports SPL 1.0/2.0/3.0/4.0/5.0 Specs

- Fully synthesizable

- Static synchronous design

- Positive edge clocking and no internal tri-states

-

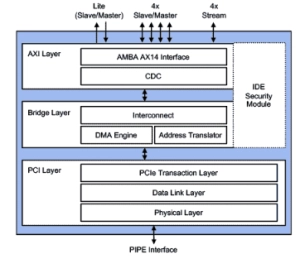

PCIe Controller for USB4 with AXI

- Internal data path size automatically scales up or down (64-, 256-, 512- bits) based on link max. speed and width for reduced gate count and optimal throughput

- Configurable pipelining enables full speed operation on Intel and Xilinx FPGA, full support for production FPGA designs up to Gen4 x8/Gen3 x16 with same RTL code – Gen5 support pending

- Stringent implementation of PCIe to AXI Ordering Rules and AXI to PCIe Ordering Rules guarantees AXI deadlock prevention

- Carefully engineered AXI bridge & AXI interconnect allows full performance on AXI interfaces

-

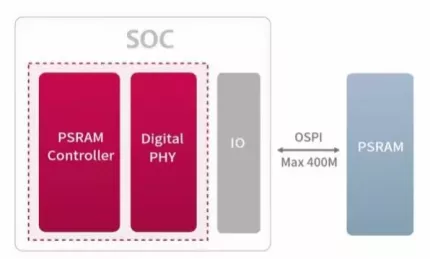

Normal Speed PSRAM Solution

- AXI3/AHB and APB3 bus interfaces

- AXI narrow/unaligned transfer, and AHB narrow transfer

- AXI burst supports INCR and WRAP

- AHB burst supports SINGLE, INCR, INCR4/8/16, WRAP4/8/16