AMBA 5 CHI IP

Filter

Compare

23

IP

from

12

vendors

(1

-

10)

-

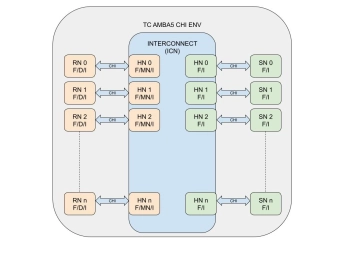

AMBA 5 CHI Verification IP

- VIP is Compliant with the latest ARM™ AMBA5 CHI.

- Support any type of network topology like Crossbar, Ring, Mesh, etc…

- Support for all types of AMBA5 CHI Nodes:

- Requester (RN-F, RN-D, RN-I)

- Home (HN-F, HN-I)

- Subordinate (SN-F, SN-I)

- Requester (RN-F, RN-D, RN-I)

-

AMBA 5 CHI Verification IP

- Compliant with the latest ARM AMBA 5 CHI specification (CHI-D).

- Supports CHI Master, Slave, Interconnect, Monitor and Checker.

- Support for Protocol, Network and Link layer communication, including flow control mechanisms across RN2HN and HN2SN links.

- Supports all CHI protocol node types:

-

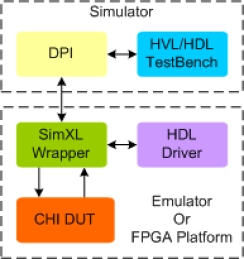

AMBA 5 CHI Synthesizable Transactor

- Compliant with the latest ARM AMBA 5 CHI specification (CHI-B).

- Supports CHI Master, Slave, Interconnect.

- Support for Protocol, Network and Link layer communication, including flow control mechanisms across RN2HN and HN2SN links.

- Supports all CHI protocol node types:

-

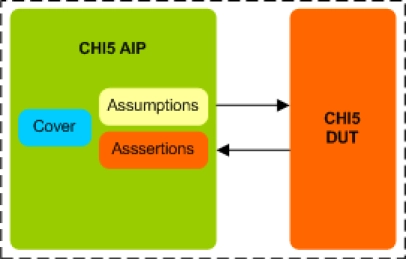

AMBA 5 CHI Assertion IP

- Specification Compliance

- Compliant with the latest ARM AMBA 5 CHI specification.

- Supports all ARM AMBA 5 CHI data widths.

- Supports for Protocol, Network and Link layer communication, including flow control mechanisms across RN2HN and HN2SN links.

-

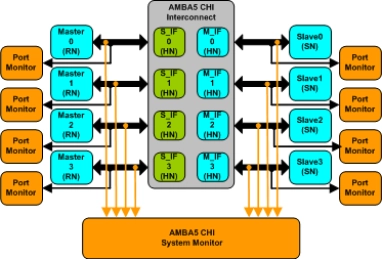

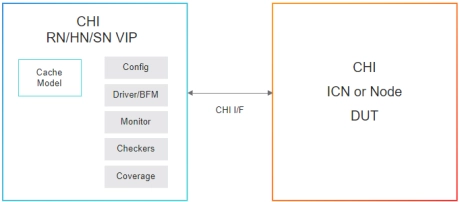

Verification IP for Arm AMBA CHI Protocol

- AMBA 5 CHI-A/B/C/D/E/F/G

- Request node, secondary node agents and monitor

- Complete port-level checks

- Supports all interface types

-

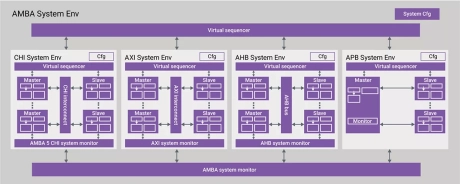

Simulation VIP for AMBA CHI

- Support testbench language interfaces for SystemVerilog, UVM, OVM, e, and SystemC

- Generates constrained-random bus traffic with predefined error injection

- Callbacks access at multiple queue points for scoreboarding and data manipulation

- Provides comprehensive checking and coverage model

-

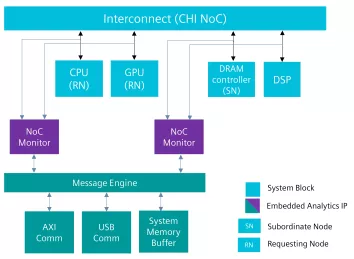

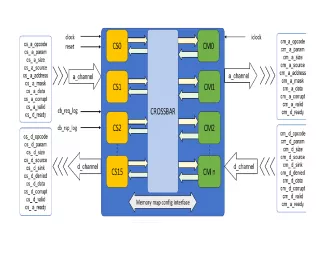

Network on Chip

- The Network on Chip (NOC) technology redefines typical NOC capabilities as it extends the on-chip network beyond chip(let) boundaries.

- The network is seamlessly extended across all chip(let)s forming a system.

- Customers basically can split up monolithic SOCs into a chiplet based system and still having a coherent system enabling a lean and efficient SW/FW stack while operating at full performance.

-

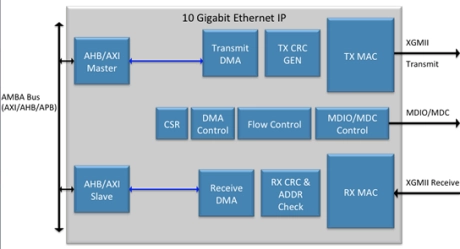

10 Gigabit Ethernet MAC IP Core

- The 10 Gigabit Ethernet (XGMAC) IP core is compliant with the Ethernet IEEE 802.3-2008 standard and provides an interface between AHB/AXI Bus and the 10 Gigabit Media Independent Interface (XGMII) using a powerful 64-bit Scatter Gather DMA.

- The 10 Gigabit Ethernet IP core is designed for applications such as integrated networking devices, host bus adapters, PCI-Express Ethernet controllers, and Ethernet adapter cards.

-

NoC Silicon IP for RISC-V based chips supporting the TileLink protocol

- Easy to integrate the NoC Silicon IP using interface

- N master and M slave ports based on customer requirement

- Supports wide range of memory map.

-

Tessent NoC Monitor

- Full transaction and trace-level visibility of traffic

- Wide range of measurements, analytics statistics: transactions, bus cycles, latency, duration, beats, concurrency