AMBA 5 CHI Verification IP

AMBA 5 CHI Verification IP provides an smart way to verify the ARM AMBA 5 CHI component of a SOC or a ASIC.

Overview

AMBA 5 CHI Verification IP provides an smart way to verify the ARM AMBA 5 CHI component of a SOC or a ASIC. The SmartDV's AMBA 5 CHI Verification IP is fully compliant with standard AMBA 5 CHI Specification and provides the following features.

AMBA 5 CHI Verification IP is supported natively in SystemVerilog, VMM, RVM, AVM, OVM, UVM, Verilog, SystemC, VERA, Specman E and non-standard verification env

AMBA 5 CHI Verification IP comes with optional Smart Visual Protocol Debugger (Smart ViPDebug), which is GUI based debugger to speed up debugging.

Key features

- Compliant with the latest ARM AMBA 5 CHI specification (CHI-D).

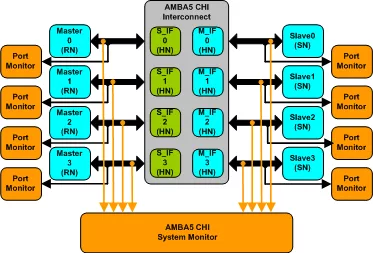

- Supports CHI Master, Slave, Interconnect, Monitor and Checker.

- Support for Protocol, Network and Link layer communication, including flow control mechanisms across RN2HN and HN2SN links.

- Supports all CHI protocol node types:

- Request Nodes (RN-F, RN-D and RN-I)

- Home Nodes (HN-F, HN-I and MN)

- Slave Nodes (SN-F and SN-I)

- Supports Link initialization as per specs.

- Support for skipping link initialization and retrying failed link initialization.

- Configurable credit including dynamic and pre-allocated credit control.

- Cache model support in Master and Interconnect (programmable). Monitor has backdoor access to these cache models.

- Support for Speculative read and Snoop filtering.

- Support for all Transaction types and Opcodes.

- Supports Direct Memory Transfer and Direct Cache Transfer.

- Supports Exclusive accesses, Cache Stashing, DVM Operations.

- Supports Deallocating transactions, Poison and Data Check.

- Supports all ARM AMBA 5 CHI data widths.

- Support for Request transactions with/without a Retry and cancelling of transactions.

- Ability to issue multiple outstanding Non-snoopable/Snoopable transactions.

- Programmable Protocol flit delays and different channels delays. Interconnect has the ability to replicate RN/SN inserted delays.

- Supports all write/read responses and snoop responses.

- Fine grain control of below:

- Requester transaction including main memory access

- Completer response to a Requester transaction and Requester acknowledgment/response to Completer's response

- Interconnect generated snoop transaction to Snooped RNs

- Interconnect generated main memory access transactions.

- Snooped RN response to a snoop transaction.

- Supports fine grain control of response per address or per transaction.

- Device and Normal memory types support.

- Support for ordering of transactions/responses and reordering of data packets.

- Support for error injection during Link initialization.

- Ability to inject errors during transfers.

- Supports constrained randomization of protocol attributes.

- Programmable Timeout insertion.

- Supports FIFO memory.

- Rich set of configuration parameters to control CHI functionality.

- On-the-fly protocol and data checking including port level and system level checks.

- Notifies the testbench of significant events such as transactions, warnings, timing and protocol violations.

- Built in coverage analysis.

- Transaction logging and Performance Reporting support.

- Callbacks in Master, Slave, Interconnect and Monitor for various events.

- Status counters for various events on bus.

- AMBA5 CHI Verification IP comes with complete testsuite to test every feature of ARM AMBA 5 CHI specification.

Block Diagram

Benefits

- Faster testbench development and more complete verification of AMBA 5 CHI designs.

- Easy to use command interface simplifies testbench control and configuration of master and slave.

- Simplifies results analysis.

- Runs in every major simulation environment.

What’s Included?

- Complete regression suite containing all the AMBA 5 CHI testcases.

- Examples showing how to connect various components, and usage of BFM and Monitor.

- Detailed documentation of all class, task and function's used in verification env.

- Documentation also contains User's Guide and Release notes.

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about Coherency IP core

CCIX Coherency: Verification Challenges and Approaches

Cache Coherency Is the New Normal

Increased CHI Coherency Verification Challenges

Fast, Thorough Verification of Multiprocessor SoC Cache Coherency

Co-Designed Cache Coherency Architecture for Embedded Multicore Systems

Frequently asked questions about Coherency Interconnect IP cores

What is AMBA 5 CHI Verification IP?

AMBA 5 CHI Verification IP is a Coherency IP core from SmartDV Technologies listed on Semi IP Hub.

How should engineers evaluate this Coherency?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Coherency IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.