5G FEC IP

Filter

Compare

20

IP

from

11

vendors

(1

-

10)

-

5G Polar Intel® FPGA IP

- The 5G Polar Intel® FPGA IP implements a forward error correction (FEC) encoder and decoder based on polar codes compliant with the 3rd Generation Partnership Project (3GPP) 5G specification for integration into your wireless design

- Polar codes represent an emerging class of error correction supporting the high throughput requirements for 5G new radio (NR).

-

NR-5G Polar Decoder and Encoder

- The Forward Error Correction (FEC) sub-system is one of the essential basing blocks in any communication systems so a powerful FEC code is needed.

- The New Radio (NR) FEC for the control channel is proposed to be designed based on Polar codes allowing close to the Shannon limit/Capacity operation.

- The Polar code successive cancellation decoding process as needed for 3GPP physical layer standard.

-

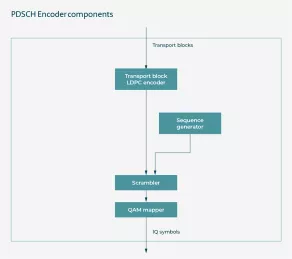

PDSCH Encoder for 3GPP 5G NR

- The PDSCH Encoder and PUSCH Decoder products simplify the creation of high performance 5G NR implementations.

- PDSCH Encoder features the new QAM mapper and Scrambler functionality. These are integrated with LDPC encoder chain and transport block chain components.

- PDSCH encoder has a configurable IQ parallelism for improved performance per clock.

- The functions included are CRC, Segmentation, LDPC encode, Rate matching, Integrated HARQ, Concatenation, Scrambling and Modulation.

-

LDPC Encoder / Decoder for 5G and 6G NTN PHY

- AccelerComm LDPC provides licensable, 3GPP-compliant encoder and decoder IP cores optimised for terrestrial, transparent NTN, and regenerative satellite PHY architectures.

- Its high-throughput, low-latency design is FPGA- and ASIC-ready, with area-efficient implementations suited to SWaP-constrained satellite payloads and high-density ground infrastructure alike.

-

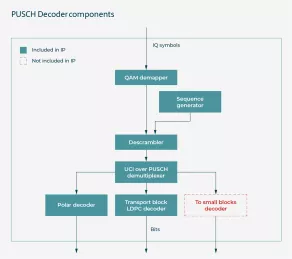

PUSCH Decoder for 3GPP 5G NR

- Complete implementation of the relevant 3GPP standard

- Improved BLER for UCI control data

-

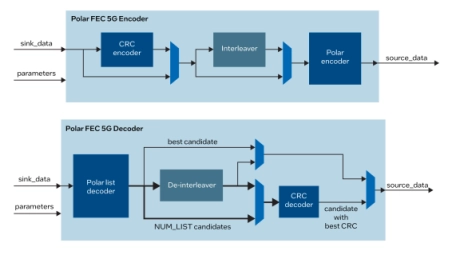

Generic Polar FEC Encoder and Decoder

- Fully-pipelined architecture

- Support for systematic and non-systematic encoding

- Support for coded block lengths of up to 1024 bits

- Support for a wide variety of

-

Software Defined Radio for high end 4G/ 5G and large MIMO application

- 8x8 Transmit and Receive Antennas support

- TI Multi-core communication processor, 1.2 GHz

- 8 C66X DSP cores and 4 ARM cores

- NOR flash – 32MB, NAND Flash – 512MB

-

Soft-Decision FEC Integrated Block

- Function configurable between either:

- Peak throughput of the order:

-

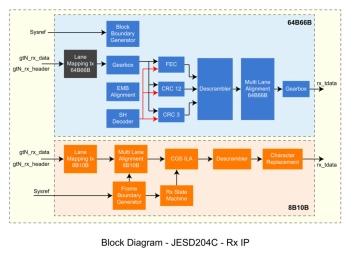

JESD204C Transmitter and Receiver

- With the addition of error correction and Detection(FEC, CRC), cutting-edge instrumentation and other applications can operate without any errors.

- Offers better DC balance, clock recovery and data alignment compared to JESD204B.

- The bit overhead is 3.125% which is much smaller than JESD204B (~ 25%).

- Provides interface for serializing devices from some system designs, reducing space, power, and cost.

-

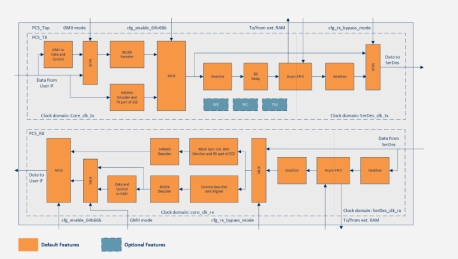

Ethernet PCS 1G/2.5G/5G/10G/25G & CPRI 7.0

- A combined silicon agnostic implementation of the PCS layer compliant with Ethernet standard IEEE 802.3-2018 and CPRI Specification V7.0 based solution

- The IP-core supports 1G, 2.5G, 5G, 10G, and 25G Ethernet data rates as well as CPRI data rate option 1 (614.14M) to option 10 (24.33024G).