JESD204C Transmitter and Receiver

Logic Fruit Technologies has developed a JESD204C RTL IP supporting lane rates up to 32 Gbps for high-bandwidth applications.

Overview

Logic Fruit Technologies has developed a JESD204C RTL IP supporting lane rates up to 32 Gbps for high-bandwidth applications. It features improved efficiency with 64B66B and 8B10B link layers, error correction (FEC), better DC balance, and reduced overhead (3.125%). This IP is ideal for 5G, medical, and military applications, ensuring deterministic latency.

Key features

- With the addition of error correction and Detection(FEC, CRC), cutting-edge instrumentation and other applications can operate without any errors.

- Offers better DC balance, clock recovery and data alignment compared to JESD204B.

- The bit overhead is 3.125% which is much smaller than JESD204B (~ 25%).

- Provides interface for serializing devices from some system designs, reducing space, power, and cost.

- It supports interface requirements of high megabit and Gigabit data rates for various applications such as 5G cellular equipments, test equipments, medical devices, military warfare and so on.

- Mechanism to achieve Deterministic latency across the serial link.

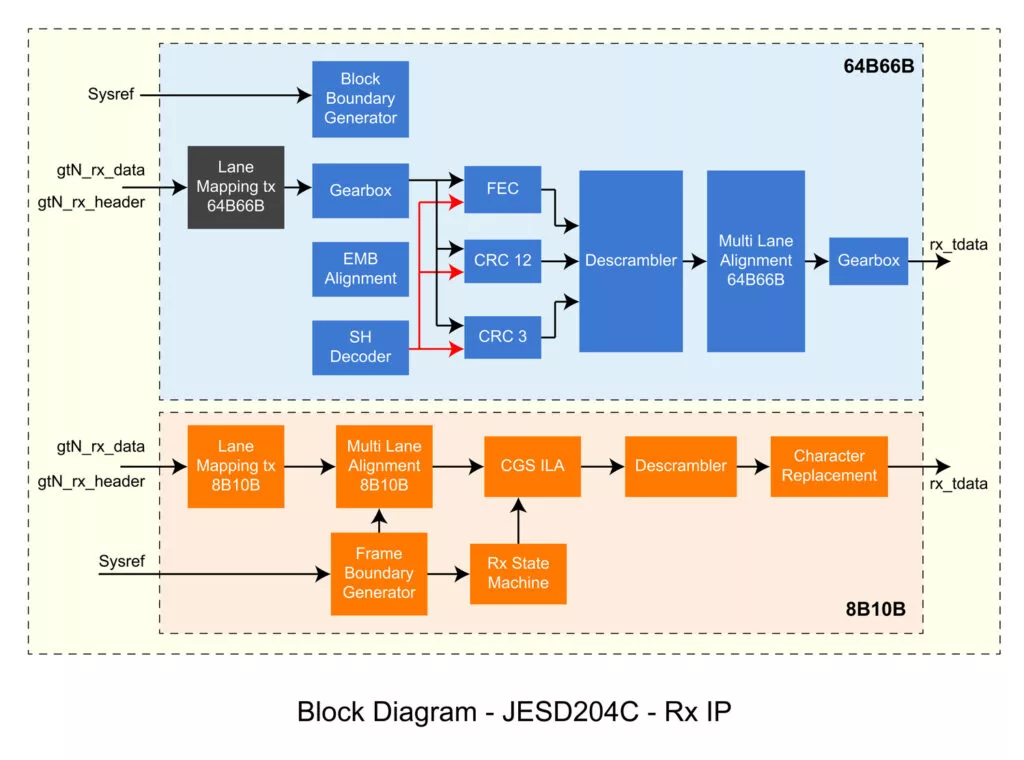

Block Diagram

Benefits

- With the addition of error correction and Detection(FEC, CRC), cutting-edge instrumentation and other applications can operate without any errors.

- Offers better DC balance, clock recovery and data alignment compared to JESD204B.

- The bit overhead is 3.125% which is much smaller than JESD204B (~ 25%).

- Provides interface for serializing devices from some system designs, reducing space, power, and cost.

- It supports interface requirements of high megabit and Gigabit data rates for various applications such as 5G cellular equipments, test equipments, medical devices, military warfare and so on.

- Mechanism to achieve Deterministic latency across the serial link.

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about JESD204 IP core

Multiple ways JESD204 performs bitstream alignment

Bridging Analog and Digital worlds at high speed with the JESD204 serial interface

UCIe D2D Adapter Explained: Architecture, Flit Mapping, Reliability, and Protocol Multiplexing

Smarter ASICs and SoCs: Unlocking Real-World Connectivity with eFPGA and Data Converters

What is JESD204C? A quick glance at the standard

Frequently asked questions about JESD204 IP cores

What is JESD204C Transmitter and Receiver?

JESD204C Transmitter and Receiver is a JESD204 IP core from Logic Fruit Technologies listed on Semi IP Hub.

How should engineers evaluate this JESD204?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this JESD204 IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.