32-Bit RISC Processor IP

Filter

Compare

44

IP

from

11

vendors

(1

-

10)

-

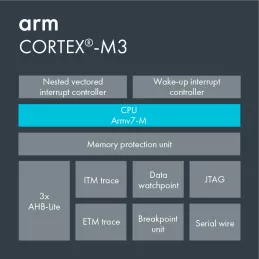

32-bit RISC Processor To Deliver High Performance In Low-Cost Microcontroller Applications

- Powerful debug and non-intrusive real-time trace - Comprehensive debug and trace features dramatically improve developer productivity. It is extremely efficient to develop embedded software with proper debug.

- Memory Protection Unit (MPU) - Software reliability improves when each module is allowed access only to specific areas of memory required for it to operate. This protection prevents unexpected access that may overwrite critical data.

- Integrated nested vectored interrupt controller (NVIC) - There is no need for a standalone external interrupt controller. Interrupt handling is taken care of by the NVIC removing the complexity of managing interrupts manually via the processor.

- Thumb-2 code density - On average, the mix between 16bit and 32bit instructions yields a better code density when compared to 8bit and 16bit architectures. This has significant advantages in terms of reduced memory requirements and maximizing the usage of precious on-chip Flash memory.

-

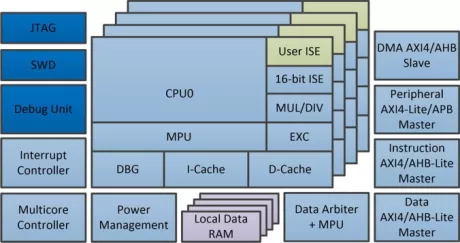

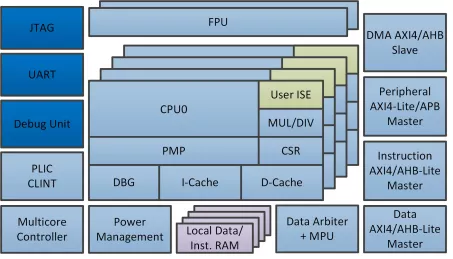

32-bit High Performance Single/Multicore RISC Processor with code compression

- High Performance 32-bit RISC CPU

- Proprietary 6-stage pipeline

- 16-bit code compression

- Single or multicore implementation

-

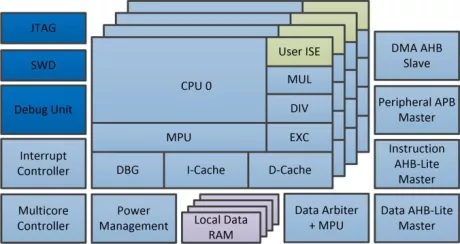

32-bit High Performance Single/Multicore RISC Processor

- High Performance 32-bit RISC CPU

- Proprietary 6-stage pipeline

- Single or multicore implementation

- Up to 1.37 DMIPS/MHz/Core

-

32-bit High Performance RV32GC Single/Multicore RISC Processor

- High Performance 32-bit RV32GC CPU

- Proprietary 6-stage pipeline

- Single or multicore implementation

- Up to 1.38 DMIPS/MHz/Core

-

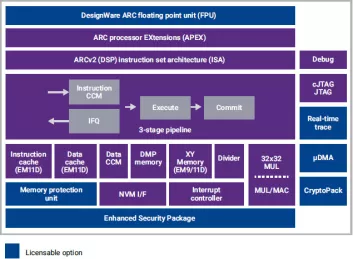

ARC EM11D Enhanced 32-bit processor core, ARCv2DSP ISA with Cache and XY Memory

- Dual 32x16 XMAC component supports up to two 32x16 MAC operations per instructions and supports all the 32x16 & dual 16x16 MAC instructions

- Dual XMAC built in shifters and 80-bit accumulators allow pseudo floating-point operations to be performed which greatly expanded dynamic range

- RAM configuration optimized for efficient area and power

- Improved system efficiency with enhanced ARM® AMBA® AXI™/AHB™ bus bridges

-

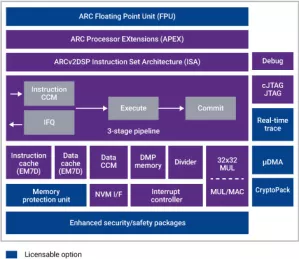

ARC EM7D DSP Enhanced 32-bit processor core with caches, ARCv2DSP ISA, for low power embedded DSP ap

- Dual 32x16 XMAC component supports up to two 32x16 MAC operations per instructions and supports all the 32x16 & dual 16x16 MAC instructions

- Dual XMAC built in shifters and 80-bit accumulators allow pseudo floating-point operations to be performed which greatly expanded dynamic range

- RAM configuration optimized for efficient area and power

- Improved system efficiency with enhanced ARM® AMBA® AXI™/AHB™ bus bridges

-

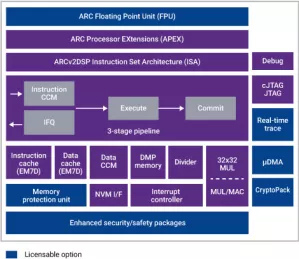

ARC EM5D Enhanced 32-bit processor core, ARCv2DSP ISA, for low power embedded DSP applications

- Dual 32x16 XMAC component supports up to two 32x16 MAC operations per instructions and supports all the 32x16 & dual 16x16 MAC instructions

- Dual XMAC built in shifters and 80-bit accumulators allow pseudo floating-point operations to be performed which greatly expanded dynamic range

- RAM configuration optimized for efficient area and power

- Improved system efficiency with enhanced ARM® AMBA® AXI™/AHB™ bus bridges

-

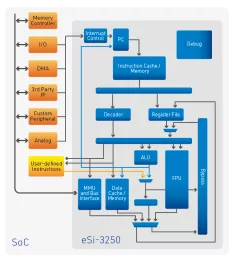

High-performance 32-bit RISC CPU

- 32-bit RISC architecture

- 16 or 32 general purpose registers

- 104 basic instructions and 10 addressing modes

-

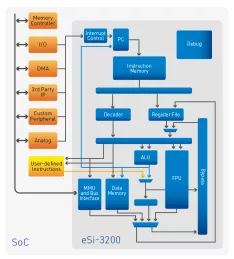

Compact, low-power 32-bit RISC CPU

- 32-bit RISC architecture

- 16 or 32 general purpose registers

- 104 basic instructions and 10 addressing modes

- Optional IEEE 754 floating point unit (FPU)

-

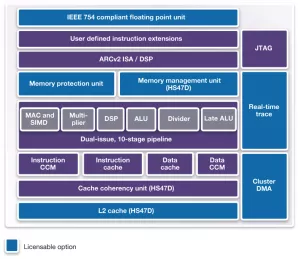

ARC HS47D 32-bit, dual-issue processor core, ARCv2DSP ISA, with 100+ DSP instructions and I&D cache

- Dual 32x16 XMAC component supports up to two 32x16 MAC operations per instructions and supports all the 32x16 & dual 16x16 MAC instructions

- Dual XMAC built in shifters and 80-bit accumulators allow pseudo floating-point operations to be performed which greatly expanded dynamic range

- RAM configuration optimized for efficient area and power

- Improved system efficiency with enhanced ARM® AMBA® AXI™/AHB™ bus bridges