100G Ethernet MAC IP

Filter

Compare

91

IP

from

19

vendors

(1

-

10)

-

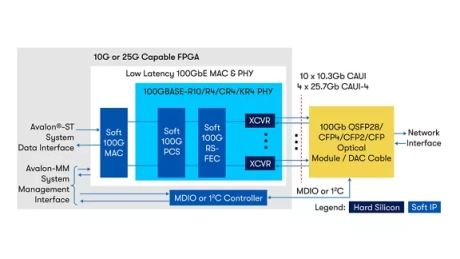

Low Latency Ethernet 100G MAC and PHY Intel® FPGA IP Core

- Intel® offers ultimate flexibility, scalability, and configurability with the Low Latency 100G Ethernet Intel® FPGA IP core targeted to network infrastructure and data centers.

- The Low Latency 100G Ethernet Intel® FPGA IP core is compliant with the IEEE 802.3ba-2010 standard, it includes a media access control (MAC), PHY, physical coding sublayer (PCS), physical medium attachment (PMA), and an optional forward error correction (FEC) block.

- It also includes IEEE 1588v2 timestamping support and the capability to drive backplanes on supported Intel® Stratix® and Intel® Arria® FPGAs. This IP can be used for chip-to-chip interfaces using copper interconnect or optical transceiver modules

-

High Speed Ethernet 100G MAC IP

- Supports all required features of the IEEE 802.3bs specification

- Supports IEEE-managed objects, IETF MIB-II and RMON for management applications

- Application interface includes the Synopsys native interface 512-bit or 1024-bit FIFO for more than 200G operation

- Designed to be used with Synopsys 100G/200G/400G/800G Ethernet PCS IP

-

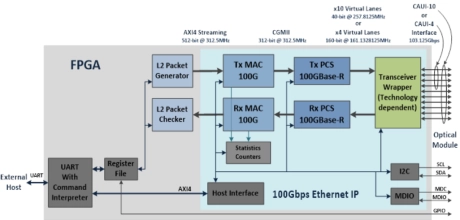

100G Ethernet Solution (MAC + 100GBase-R PCS)

- Implements the full 802.3 specification with preamble/SFD generation, frame padding generation, CRC generation and checking on transmit and receive respectively.

- Implements 802.3bd specification with ability to generate and recognize PFC pause frames (optional)

- Implements reconciliation sublayer functionality with start and terminate control characters alignment, error control character and fault sequence insertion and detection.

- Implements Deficit Idle Count (DIC) mechanism to ensure maximum possible throughput at the transmit interface.

-

100G Only 320-bit Ethernet MAC + PCS @ 312.5MHz Solution; 4x25

- MAC Core Features

- PCS Core Features (Common)

- PCS Core Features (CAUI-4 Option)

- PCS Core Features (CAUI-10 Option)

-

100G Only 320-bit Ethernet MAC + PCS @ 312.5MHz Solution; 10x10

- MAC Core Features

- PCS Core Features (Common)

- PCS Core Features (CAUI-4 Option)

- PCS Core Features (CAUI-10 Option)

-

UltraScale Integrated 100G Ethernet MAC/PCS

- Supports 10 lanes x10.3125 CAUI-10, 4 lanes x25.78125G CAUI-4 or dynamically switchable CAUI-4 and CAUI-10 mode

- No charge license key enabled

- 1588 1-step and 2-step hardware time stamping

- Allows insertion of custom logic such as RS-FEC between the 100G Ethernet integrated block and GT

-

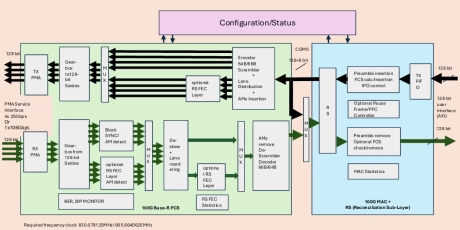

100G MAC/PCS Ultra Ethernet

- The IP integrates MAC Layer, RS Sub-Layer and 100G PCS Base-R cores according to IEEE 802.3 standard to provide seamless connection between an application and serdes interfaces

- 128-bit interface for TX and RX between MAC and the application Serdes interface – configurable to support PAM2 and PAM 4

-

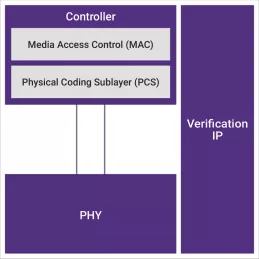

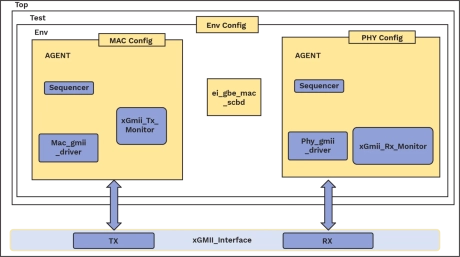

100G Ethernet Verification IP

- The 100G Ethernet Verification IP (VIP) offers a robust and high-performance solution for validating the critical MAC-to-PCS datapath in 100 Gigabit Ethernet systems.

- Designed to ensure protocol compliance, the VIP facilitates the generation, transmission, reception, and monitoring of various Ethernet MAC frame types, all while adhering to IEEE 802.3ba and related standards.

- Whether you are working on IP, subsystem, or SoC-level verification, this VIP is your go-to solution for comprehensive Ethernet testing.

-

100 G Ethernet MAC & PCS IP Core

- The 100 Gbps Ethernet IP solution offers a fully integrated IEEE802.3ba compliant package for NIC (Network Interface Card) and Ethernet switching applications.

- Ethernet IP solution implements two user (application) side interfaces. The register configuration and control port is a 32-bit AXI4-Lite interface.

-

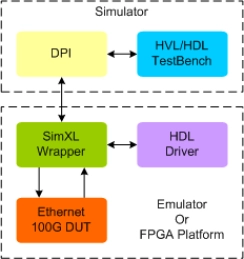

Ethernet 100G Synthesizable Transactor

- Supports 100G as per 802.3ba and 802.3bj:

- Supports CGMII

- Supports 100GBase-KR10/

- Supports 100GBase-KR4