Data Fusion IP Subsystem

IoT applications increasingly require sensing capabilities that extend beyond what traditional sensors provide.

Overview

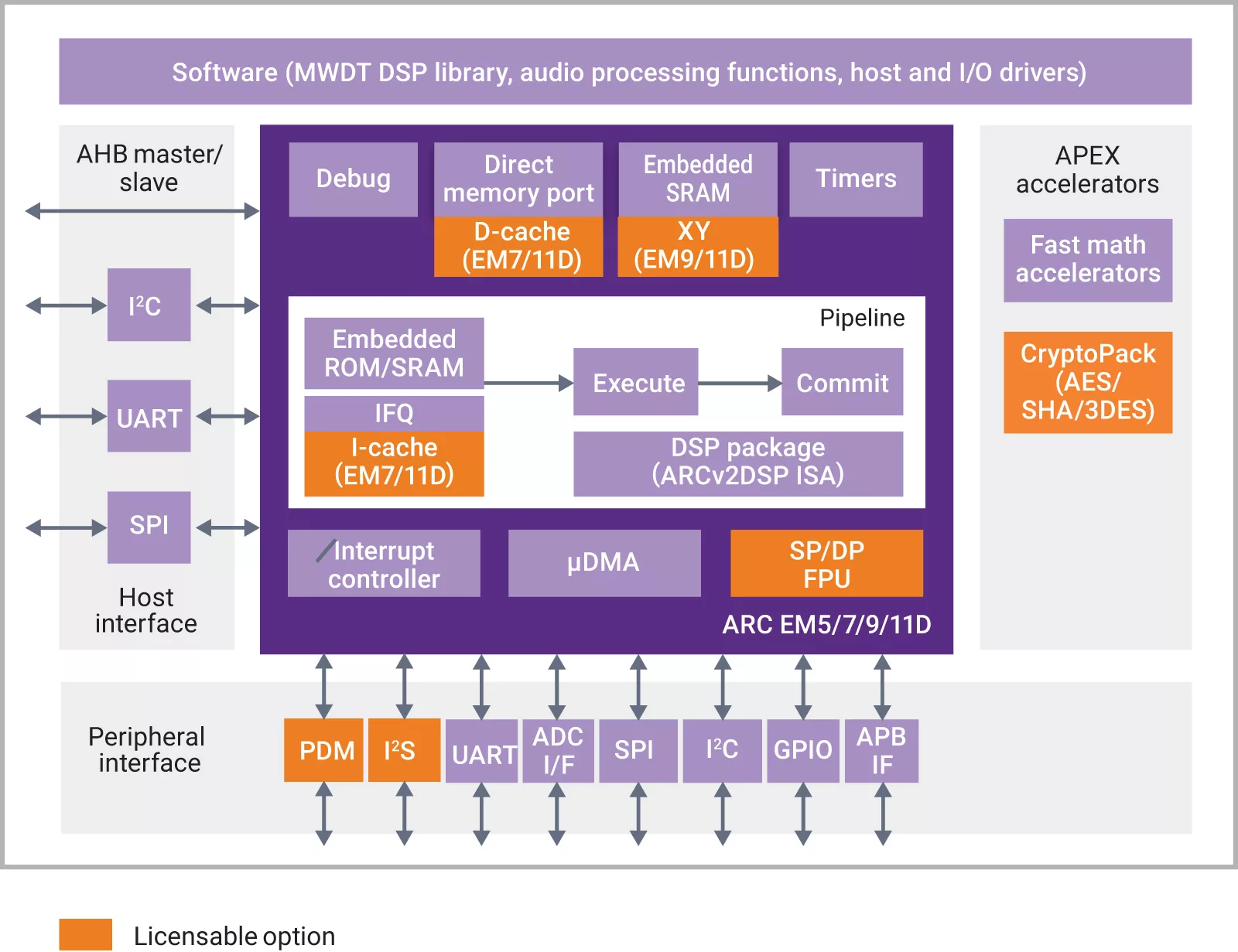

IoT applications increasingly require advanced sensing capabilities that extend beyond what traditional sensors provide. Functions such as face detection, voice and gesture recognition require an efficient combination of RISC and DSP processing. The ARC® Data Fusion IP Subsystem is a complete, pre-verified, hardware and software solution optimized for a wide range of ultra-low power IoT applications. It is designed for fast and easy integration within a larger system context.

The fully configurable ARC Data Fusion IP Subsystem includes the choice of a low gate count and energy-efficient ARC EM5D, EM7D, EM9D or EM11D processor for both RISC and DSP processing, accompanied by an extensive collection of I/O functions and fast math (trigonometric) accelerators. The software libraries of the subsystem contain small-footprint drivers for all I/O, plus DSP functions supporting signal processing. It also includes an audio processing software library of common functions, including gain control, mixer and sample rate converter. Tightly coupled PDM and I2S peripherals simplify integration of external audio devices and the hardware PDM interface implementation is 6X more energy efficient than the equivalent software implementation, with minimal gate count impact. The audio library and peripherals (PDM, I2S) are part of a voice/speech licensable option. The integrated solution is optimized for “always on” data fusion combining sensor, voice, gesture and audio processing typically implemented in IoT edge devices.

Key features

- Integrated, pre-verified hardware and software IP subsystem

- ARC EM processors with cache and DSP extensions deliver extremely low gate count and highly efficient processing performance

- Extensive library of software DSP functions enable sensor signal processing

- Hardware accelerators boost performance efficiency and reduce power consumption

- Integrated peripherals provide a wide range of SoC connectivity options for SoC/MCUs

- Options supporting higher performance voice/speech and sensor requirements

Block Diagram

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about Mixed Signal Subsystem IP core

Mixed Signal Design & Verification Methodology for Complex SoCs

Systematic approach to verification of a mixed signal IP - HSIC PHY case study

Customized PMICs with OTP in automotive and IoT

Effective Optimization of Power Management Architectures through Four standard "Interfaces for the Distribution of Power"

How to specify and integrate successfully a measurement analog front-end including its power computation engine in an energy metering IC

Frequently asked questions about Mixed-Signal Subsystem IP cores

What is Data Fusion IP Subsystem?

Data Fusion IP Subsystem is a Mixed Signal Subsystem IP core from Synopsys, Inc. listed on Semi IP Hub.

How should engineers evaluate this Mixed Signal Subsystem?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Mixed Signal Subsystem IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.