Universal Asynchronous Receiver/Transmitter Module

The UARTmodule is part of Inicore's IPmodule family.

Overview

The UARTmodule is part of Inicore's IPmodule family. Universal asynchronous receiver and transmitter, using the RS232 protocol, are often used to connect peripheral devices to a central controller.

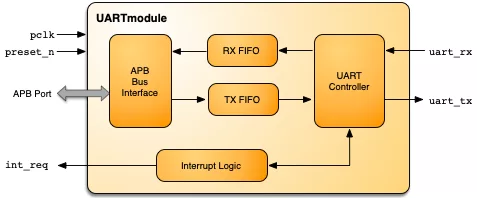

The UARTmodule has one receive and one transmit channel, receive and transmit buffers, an interrupt controller as well as a local bus interface. The built-in receive buffer is configurable in depth, therefore, enabling a gate count and application optimized implementation.

The baudrate generator uses a innovative digital controlled oscillator (DCO) to generate baudrates over a wide frequency range. With a system clock of 8MHz, all baudrates from 1200 baud to 115.2 kbaud have an accuracy of better than 0.1%!

To improve glitch rejection, the receiver uses a 3-point input sampling. Format and parity errors are detected and reported.

Implementation Features

- Supports register and SRAM based FIFO implementations.

- The Rx-FIFO size is selectable enabling the optimal device utilization

- Fully synchronous design: one clock, one global asynchronous reset.

- Technology independent implementation. This design can be used for any technology as long as timing constraints are met.

Key features

- Single channel UART

- Flexible baudrate generator

- Status and error registers

- Scalable RxFIFO (2/4/8/16 bytes deep)

- Double buffered TxFIFO

- 7-bit or 8-bit format

- 1 or 2 stopbits

- Parity enable, even or odd

- Receive timeout counter

- Local loop back mode

- Local interrupt controller

- Industry standard AMBA APB host interface

- Full synchronous design

- Technology independent, vendor independent

Block Diagram

Benefits

- For gate-count optimization, the core can be configured to disable the configuration register read-back path. Synthesis options are included to use the core in 8, 16 or 32-bit systems. With a separate APB wrapper, the core can be used in ARM subsystems

What’s Included?

- VHDL or Verilog RTL Source Code

- Functional Testbench

- Synthesys Script

- Data Sheet

- User Guide

- Hotline Support by means of phone, fax and e-mail

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about UART IP core

Capturing a UART Design in MyHDL & Testing It in an FPGA

Integrating Post-Quantum Cryptography (PQC) on Arty-Z7

How to design secure SoCs, Part V: Data Protection and Encryption

Not all overvoltage tolerant GPIOs are the same

CAST Provides a Functional Safety RISC-V Processor IP for Microchip FPGAs

Frequently asked questions about UART IP cores

What is Universal Asynchronous Receiver/Transmitter Module?

Universal Asynchronous Receiver/Transmitter Module is a UART IP core from Inicore, Inc. listed on Semi IP Hub.

How should engineers evaluate this UART?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this UART IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.