High-Level Data Link Controller

Inicore's iniHDLC family of High-Level Data Link Controller (HDLC) cores consist of a Receiver (FPR: From Primary Rate) and a Tra…

Overview

Inicore's iniHDLC family of High-Level Data Link Controller (HDLC) cores consist of a Receiver (FPR: From Primary Rate) and a Transmitter (TPR: To Primary Rate) unit. These single channel HDLC controllers handle all interframe flags, delimiting flags and Frame Check Sequence (FCS) pattern. The FCS is calculated using a CRC-16 polynomial.

The HDLC protocol has several subsets (e.g., Q.921, Q922, X.25 etc.). The structure of a frame (header, trailer, FCS, stuffing/destuffing) is the same but the procedures for Commands, Responses and Abort Conditions are different and are handled by software. iniHDLC cores can be used within the whole HDLC subset.

The iniHDLC cores are a synthesiszable, flexible, and structured VHDL implementation of the HDLC protocol. The cores are designed for easy interfacing to custom buffers (e.g., FIFO, DMA-Interface).

Key features

- Single Port Interface

- Transparent Mode

- Start- and Stopflag Generation/Detection

- Frame Check Sequence Generation/Verification (CRC-16)

- Built-in Bit Stuffing/Destuffing

- Frame Status Signalling

- Clock to Baud Ratio up to 1:1

- Supporting Protocols: Q.921(LAPD) ISDN, Q.922 Frame Relay, X.25 (LAPB) PBX , WAN...and more

- Flexible I/O Interface towards FIFO, uP, RAM and DMA

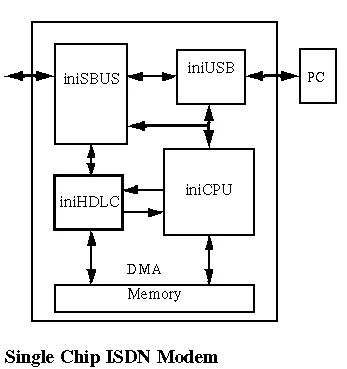

Block Diagram

Benefits

- Full synchronous operation

- Easy interfacing to customers requirements such as

- Interrupt controled data transfer

- Direct memory access using built-in DMA controller

- On-chip dual-port memory for temporary buffering of frame

What’s Included?

- VHDL or Verilog RTL Source Code

- Functional Testbench

- Synthesys Script

- Data Sheet

- User Guide

- Hotline Support by means of phone, fax and e-mail

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about HDLC IP core

CAST Provides a Functional Safety RISC-V Processor IP for Microchip FPGAs

D32PRO, scalable & royalty free 32-bit CPU

Generic Driver Model using hardware abstraction and standard APIs

Synthesizable verification IP speeds design cycle

Synthesizable Verification IP

Frequently asked questions about HDLC IP cores

What is High-Level Data Link Controller?

High-Level Data Link Controller is a HDLC IP core from Inicore, Inc. listed on Semi IP Hub.

How should engineers evaluate this HDLC?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this HDLC IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.