AMBA AXI IP

Welcome to the ultimate AMBA AXI IP hub! Explore our vast directory of AMBA AXI IP

All offers in

AMBA AXI IP

Filter

Compare

197

AMBA AXI IP

from

31

vendors

(1

-

10)

-

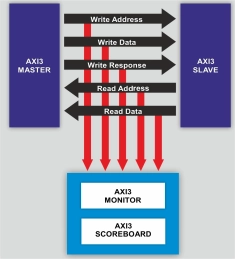

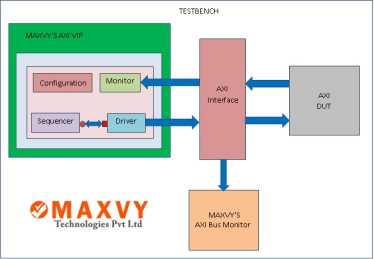

AMBA AXI3 Verification IP

- The AMBA AXI3 Verification IP provides an effective & efficient way to verify the components interfacing with AMBA® AXI3 bus of an IP or SoC.

- The AMBA AXI3 VIP is fully compliant with standard AMBA® AXI3 specification from ARM.

- This VIP is a light weight VIP with easy plug-and-play interface so that there is no hit on the design cycle time.

-

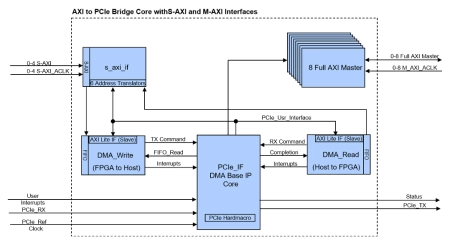

AXI Bridge for PCIe IP Core

- The AXI Bridge for PCIe IP core is the IP solution with a powerful mix of multiple industry standard memory mapped AXI Interfaces.

- The AXI Bridge IP core translates the AXI4 memory read or writes to PCI-Express Transaction Layer Packets and translates PCIe memory read and write requests to AXI4 transactions.

- All interfaces support fully parallel operation without any interferences. Interfaces that are not required can be turned off individually and do not occupy logic resources.

-

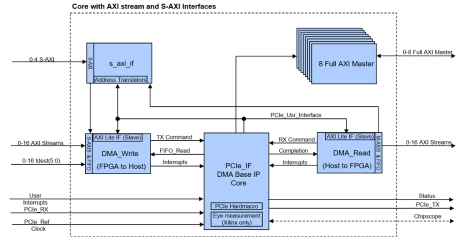

AXI Bridge with DMA for PCIe IP Core

- The AXI Bridge with DMA IP core is the ultimate PCIe DMA IP solution with a powerful mix of multiple industry standard AXI Interfaces.

- AXI Stream interfaces allow continuous data streaming from FPGA to Host or from Host to FPGA. S-AXI Memory mapped interfaces allow easy data access of remote memories in order to realize shared memory access or per to peer applications.

-

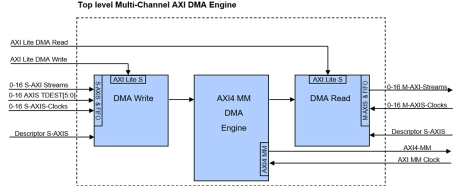

Multi-Channel AXI DMA Engine

- The Multi-Channel AXI DMA engine IP Core for AXI4 is a powerful programmable AXI Stream to AXI memory mapped bridge with sophisticated data addressing options.

- These features allow data accesses on a tile basis in order to address regions of interest (ROI) based applications like stereo cameras, 2D picture compression algorithms and others.

-

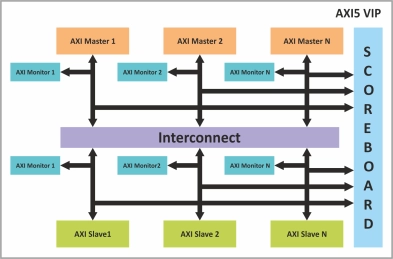

AMBA AXI5 Verification IP

- AXI5 VIP is Compliant with the latest ARM™ AMBA AXI5 & AXI5 lite.

- It is also compatible with AXI3, AXI4 Protocol Specification v2.0 referred to as AXI4 and AXI4-Lite.

- Supports Unique ID feature for both read and write transactions.

- Supports MTE(Memory Tagging Extension) feature to detect memory safety violations.

-

AMBA AXI4 Verification IP

- Compliant to AMBA® AXI4 specifications from ARM and

- supports for all variants of AXI4, AXI4-Lite and AXI4 Stream.

- Support for all type of AMBA AXI4 devices.

- Strong protocol checking Bus Monitor which also provides statistics of the transactions.

-

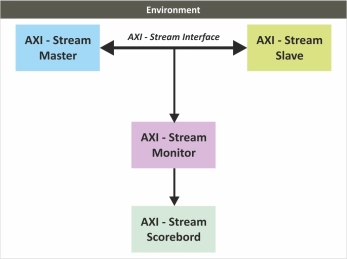

AMBA AXI STREAM Verification IP

- Compliant with AMBA® AXI5- Stream and AXI4-Stream.

- Support for all types of AMBA AXI5-Stream and AXI4-STREAM components.

- Supports parameterized data widths.

- Supports byte stream transmission number of data and null bytes.

-

AXI Verification IP

- The AMBA-AXI VIP provides a complete solution for verification of AMBA-AXI protocol version 2.0

- The AXI verification IP is fully compatible with standard AXI 3 protocol

- This VIP is supported natively in System Verilog UVM

-

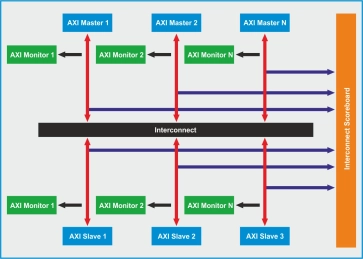

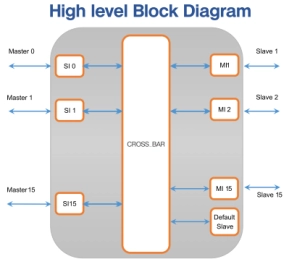

AXI Interconnect

- The AXI MATRIX-IP component is a multi-layer interconnect implementation of the AXI protocol, which is designed for high-performance, high-frequency system designs.

- AXI MATRIX-IP is highly configurable with the capacity to handle up to 16 Masters and Slaves. IP can be configured to support AXI3, AXI4-Lite or AXI4

-

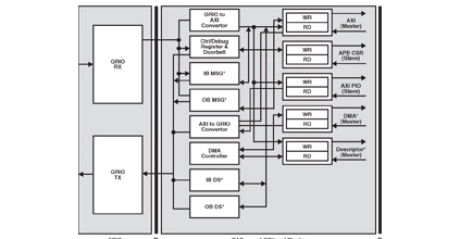

RapidIO to AXI Bridge (RAB)

- The RapidlO-AXI Bridge (RIO-AXI Bridge) is a highly flexible and configurable IP used along with the native RapidlO Controller (GRIO) to provide RapidlO interface on one side and AXI interface on the system side.

- The Bridge has been architectured to interface with a RapidlO controller used as a Host or device.

- The RIO-AXI BRIDGE uses high speed multi-channel DMA Messaging and data streaming controllers to match the bandwidth requirements of the RIO solution.