Other

All offers in

Other

Filter

Compare

17

Other

from

9

vendors

(1

-

10)

-

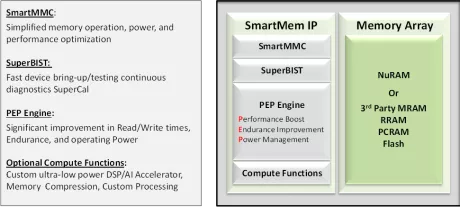

SmartMem Subsystem IP

- Fully synthesizable and configurable memory subsystem IP that enables significant improvement in power, performance and endurance not only for NuRAM but also other third party MRAMs as well as RRAM, PCRAM and Flash

-

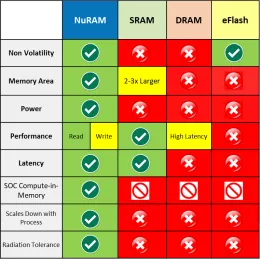

Low Power Memory IP

- State-of-the-art, patented memory technology based on industry proven MRAM.

- Fast access times and extremely low leakage power make it an attractive upgrade to traditional SRAM or nvRAM as well as embedded Flash.

-

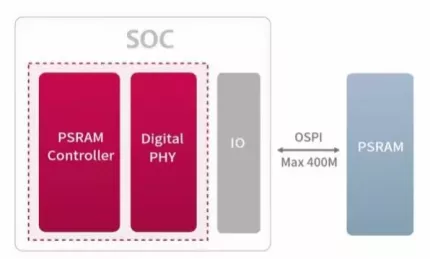

Normal Speed PSRAM Solution

- AXI3/AHB and APB3 bus interfaces

- AXI narrow/unaligned transfer, and AHB narrow transfer

- AXI burst supports INCR and WRAP

- AHB burst supports SINGLE, INCR, INCR4/8/16, WRAP4/8/16

-

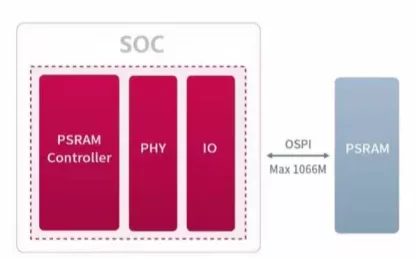

High Speed PSRAM Solution

- High Speed PSRAM Solution

- ? High Speed PSRAM PHY

- ? Operating range of 200MHz (400Mbps) to 533MHz (1066Mbps) in PSRAM mode

- ? PHY Utility Block (PUBL) component

-

Serial Peripheral Interface (SPI) Controller

- Dolphin Technology provides Serial Peripheral Interface (SPI) IP which enables an AHB/APB host to access a serial device at high-speed through the SPI interface.

- The controller supports both Master and Slave modes and consists of a DMA controller to enhance the system performance.

- The IP can be used in applications such as flash memory card and digital camera.

-

Memory Compiler in TSMC (16nm,22nm,28nm,40nm,55nm,90BCD+,110nm,152nm,180BCD)

- Synchronous read/write operation

- Low leakage current and lower operation power consumption

- Minimum metal layer requirement: 4/3 metal layers

- High density layout structure and small area design

-

GCRAM, the highest-density on-chip embedded memory in standard CMOS

- High-density bitcell offering up-to 2X area reduction over high-density 6T SRAM.

- Full logic compatibility with standard CMOS, no additional process steps or cost.