FIFO/LIFO IP

Welcome to the ultimate FIFO/LIFO IP hub! Explore our vast directory of FIFO/LIFO IP

All offers in

FIFO/LIFO IP

Filter

Compare

6

FIFO/LIFO IP

from

3

vendors

(1

-

6)

-

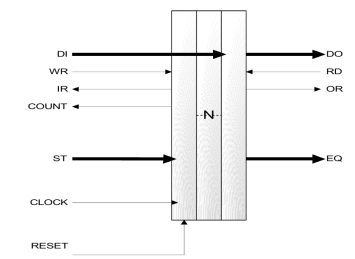

Searchable Synchronous FIFO

- The FIFO-CAM controls are designed to operate over a wide range of clock frequencies.

- The interface signals are fully synchronous; no asynchronous signals are present on either side.

- Only reset may be asynchronous in that it may be asserted asynchronously and synchronized internally to the clock.

-

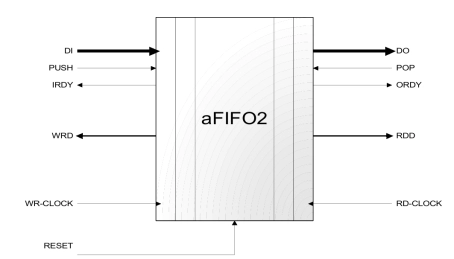

Asynchronous FIFO with configurable flags and counts

- The aFIFO2 controls are designed to ensure hazard free clock domain crossing between the read and write ports.

- Only single control lines are re-synchronized between the two clock domains ensuring hazard free operation.

- The requirement for Gray coded addressing is thus eliminated. A wide range of clock frequencies and relative frequencies between read and write ports are fully tolerated.

-

Synchronous FIFO with second read/write port as companion to A2_CAM_FIFO

- Synchronous FIFO with second read/write port as companion to A2_CAM_FIFO

-

DO-254 FIFO Generator 1.00a

- FIFO depths up to 4,194,304 words

- FIFO data widths from 1 to 1024 bits for Native FIFO configurations and up to 4096 bits for AXI FIFO configurations

- Non-symmetric aspect ratios (read-to-write port ratios ranging from 1:8 to 8:1)

- Supports Independent or common clock domains

-

FIFO Generator

- FIFO depths up to 4,194,304 words

- FIFO data widths from 1 to 1024 bits for Native FIFO configurations and up to 4096 bits for AXI FIFO configurations

- Non-symmetric aspect ratios (read-to-write port ratios ranging from 1:8 to 8:1)

- Supports Independent or common clock domains

-

AXI Streaming FIFO

- 32-bit AXI Memory Map slave interface with point to point optimizations.

- Independent internal 2 Kb TX and RX data FIFOs

- Full duplex operation.

- Provides interrupts for many error and status conditions.